แม้ว่าทรานซิสเตอร์ (BJT) จะเป็นที่นิยมใช้ในการสร้างวงจรขยายเสียง แต่ก็สามารถใช้สำหรับการสลับแอปพลิเคชันได้อย่างมีประสิทธิภาพ

สวิตช์ทรานซิสเตอร์ เป็นวงจรที่ตัวสะสมของทรานซิสเตอร์เปิด / ปิดด้วยกระแสที่ค่อนข้างใหญ่กว่าเพื่อตอบสนองต่อการสลับสัญญาณเปิด / ปิดกระแสต่ำที่สอดคล้องกันที่ตัวปล่อยฐาน

ดังตัวอย่างต่อไปนี้ การกำหนดค่า BJT สามารถใช้เป็นสวิตช์ได้ สำหรับการกลับสัญญาณอินพุตสำหรับวงจรลอจิกคอมพิวเตอร์

ที่นี่คุณจะพบว่าแรงดันเอาต์พุต Vc ตรงข้ามกับศักย์ที่ใช้กับฐาน / ตัวปล่อยของทรานซิสเตอร์

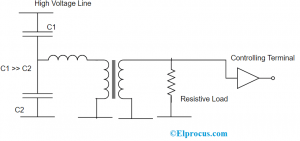

นอกจากนี้ฐานไม่ได้เชื่อมต่อกับแหล่ง DC คงที่ซึ่งแตกต่างจากวงจรที่ใช้เครื่องขยายเสียง ตัวรวบรวมมีแหล่งจ่ายไฟ DC ซึ่งสอดคล้องกับระดับการจ่ายของระบบตัวอย่างเช่น 5 V และ 0 V ในกรณีแอปพลิเคชันคอมพิวเตอร์นี้

เราจะพูดถึงวิธีการออกแบบการผกผันของแรงดันไฟฟ้านี้เพื่อให้แน่ใจว่าจุดปฏิบัติการเปลี่ยนจากการตัดไปเป็นความอิ่มตัวตามแนวโหลดได้อย่างถูกต้องดังแสดงในรูปต่อไปนี้:

สำหรับสถานการณ์ปัจจุบันในรูปด้านบนเราได้สันนิษฐานว่า IC = ICEO = 0 mA เมื่อ IB = 0 uA (เป็นการประมาณที่ดีสำหรับกลยุทธ์การก่อสร้าง) นอกจากนี้สมมติว่า VCE = VCE (sat) = 0 V แทนที่จะเป็นระดับ 0.1 ถึง 0.3 V ตามปกติ

ตอนนี้ที่ Vi = 5 V BJT จะเปิดและการพิจารณาการออกแบบจะต้องตรวจสอบให้แน่ใจว่าการกำหนดค่ามีความอิ่มตัวสูงโดยขนาดของ IB ซึ่งอาจมากกว่าค่าที่เกี่ยวข้องกับเส้นโค้ง IB ที่ใกล้เคียงกับระดับความอิ่มตัว

ดังที่สามารถอธิบายได้ในรูปด้านบนเงื่อนไขนี้เรียกร้องให้ IB มีค่ามากกว่า 50 uA

การคำนวณระดับความอิ่มตัว

ระดับความอิ่มตัวของตัวสะสมสำหรับวงจรที่แสดงสามารถคำนวณได้โดยใช้สูตร:

IC (sat) = Vcc / Rc

ขนาดของกระแสไฟฟ้าพื้นฐานในพื้นที่ที่ใช้งานอยู่ก่อนถึงระดับความอิ่มตัวสามารถคำนวณได้โดยใช้สูตร:

IB (สูงสุด) ≅ IC (sat) / βdc ---------- สมการ 1

นี่หมายความว่าในการใช้ระดับความอิ่มตัวจะต้องเป็นไปตามเงื่อนไขต่อไปนี้:

IB> IC (sat) / IC (sat) / βdc -------- สมการ 2

ในกราฟที่กล่าวข้างต้นเมื่อ Vi = 5 V ระดับ IB ที่ได้ผลลัพธ์สามารถประเมินได้ด้วยวิธีการต่อไปนี้:

หากเราทดสอบสมการ 2 ด้วยผลลัพธ์เหล่านี้เราจะได้รับ:

สิ่งนี้ดูเหมือนจะเป็นไปตามเงื่อนไขที่ต้องการอย่างสมบูรณ์ ไม่ต้องสงสัยเลยว่าค่าใด ๆ ของ IB ที่สูงกว่า 60 uA จะได้รับอนุญาตให้ป้อนผ่านจุด Q เหนือเส้นโหลดที่อยู่ใกล้กับแกนแนวตั้งมาก

ตอนนี้อ้างอิงถึงเครือข่าย BJT ที่แสดงในแผนภาพแรกในขณะที่ Vi = 0 V, IB = 0 uA และเมื่อเทียบกับ IC = ICEO = 0 mA การลดลงของโวลต์ที่เกิดขึ้นใน RC จะเป็นไปตามสูตร:

VRC = ICRC = 0 โวลต์

สิ่งนี้ทำให้เรามี VC = +5 V สำหรับแผนภาพแรกด้านบน

นอกเหนือจากแอปพลิเคชันการสลับ Logoc คอมพิวเตอร์แล้วการกำหนดค่า BJT นี้ยังสามารถใช้งานได้เช่นสวิตช์โดยใช้จุดสูงสุดเดียวกันของโหลดไลน์

เมื่อเกิดความอิ่มตัว IC ปัจจุบันมีแนวโน้มที่จะค่อนข้างสูงซึ่งจะทำให้แรงดันไฟฟ้า VCE ลดลงถึงจุดต่ำสุด

สิ่งนี้ทำให้เกิดระดับความต้านทานทั่วทั้งสองขั้วดังที่แสดงในรูปต่อไปนี้และคำนวณโดยใช้สูตรต่อไปนี้:

R (sat) = VCE (sat) / IC (sat) ตามที่ระบุในรูปต่อไปนี้

หากเราสมมติค่าเฉลี่ยทั่วไปสำหรับ VCE (sat) เช่น 0.15 V ในสูตรข้างต้นเราจะได้รับ:

ค่าความต้านทานนี้ข้ามขั้วอิซีแอลของตัวเก็บรวบรวมมีลักษณะค่อนข้างน้อยเมื่อเทียบกับความต้านทานแบบอนุกรมในหน่วยกิโลโอห์มที่ขั้วตัวสะสมของ BJT

ตอนนี้เมื่ออินพุต Vi = 0 V การสลับ BJT จะถูกตัดออกทำให้ความต้านทานของตัวปล่อยตัวสะสมเป็น:

R (ทางลัด) = Vcc / ICEO = 5 V / 0 mA = ∞Ω

สิ่งนี้ก่อให้เกิดสถานการณ์แบบวงจรเปิดในขั้วตัวปล่อยตัวเก็บรวบรวม หากเราพิจารณาค่าทั่วไป 10 uA สำหรับ ICEO ค่าของความต้านทานการตัดจะเป็นดังที่ระบุด้านล่าง:

Rcutoff = Vcc / ICEO = 5 V / 10 uA = 500 k Ω

ค่านี้ดูใหญ่มากและเทียบเท่ากับวงจรเปิดสำหรับการกำหนดค่า BJT ส่วนใหญ่เป็นสวิตช์

การแก้ตัวอย่างการปฏิบัติ

คำนวณค่าของ RB และ RC สำหรับสวิตช์ทรานซิสเตอร์ที่กำหนดค่าไว้เช่นอินเวอร์เตอร์ด้านล่างโดยให้ ICmax = 10mA

สูตรสำหรับการแสดงความอิ่มตัวของตัวสะสมคือ:

ICsat = Vcc / Rc

∴ 10 mA = 10 V / Rc

∴ Rc = 10 V / 10 mA = 1 kΩ

นอกจากนี้เมื่อถึงจุดอิ่มตัว

IB ≅ IC (sat) / βdc = 10 mA / 250 = 40 μA

สำหรับความอิ่มตัวที่รับประกันให้เลือก IB = 60 μAและใช้สูตร

IB = Vi - 0.7 V / RB เราได้

RB = 10 V - 0.7 V / 60 μA = 155 kΩ,

ปัดเศษผลลัพธ์ข้างต้นเป็น 150 kΩและประเมินสูตรข้างต้นอีกครั้งเราจะได้:

IB = Vi - 0.7 V / RB

= 10 V - 0.7 V / 150 kΩ = 62 μA,

ตั้งแต่ IB = 62 μA > ICsat / βdc = 40 μA

นี่เป็นการยืนยันว่าเราต้องใช้ RB = 150 kΩ

การคำนวณการสลับทรานซิสเตอร์

คุณจะพบทรานซิสเตอร์พิเศษที่เรียกว่าทรานซิสเตอร์สวิตชิ่งเนื่องจากอัตราการเปลี่ยนจากระดับแรงดันไฟฟ้าหนึ่งไปยังอีกระดับหนึ่งอย่างรวดเร็ว

รูปต่อไปนี้เปรียบเทียบช่วงเวลาที่เป็นสัญลักษณ์เป็น ts, td, tr และ tf กับกระแสของตัวเก็บรวบรวมของอุปกรณ์

ผลกระทบของช่วงเวลาต่อการตอบสนองความเร็วของตัวรวบรวมถูกกำหนดโดยการตอบสนองปัจจุบันของตัวรวบรวมดังที่แสดงด้านล่าง:

เวลาทั้งหมดที่จำเป็นสำหรับทรานซิสเตอร์ในการเปลี่ยนจากสถานะ 'ปิด' เป็นสถานะ 'เปิด' จะมีสัญลักษณ์เป็น t (เปิด) และสามารถกำหนดได้โดยสูตร:

t (บน) = tr + td

“วิธีทำแดมิน ”

ที่นี่ td ระบุความล่าช้าที่เกิดขึ้นในขณะที่สัญญาณการสลับอินพุตกำลังเปลี่ยนสถานะและเอาต์พุตทรานซิสเตอร์กำลังตอบสนองต่อการเปลี่ยนแปลง เวลา tr บ่งชี้ความล่าช้าในการสลับขั้นสุดท้ายจาก 10% ถึง 90%

เวลาทั้งหมดที่ใช้โดย bJt จากสถานะเปิดเป็นสถานะปิดจะแสดงเป็น t (ปิด) และแสดงโดยสูตร:

t (ปิด) = ts + tf

ts กำหนดเวลาในการจัดเก็บในขณะที่ tf ระบุเวลาตกจาก 90% ถึง 10% ของค่าเดิม

Refferrng เป็นกราฟด้านบนเพื่อวัตถุประสงค์ทั่วไป BJT ถ้าตัวเก็บกระแส Ic = 10 mA เราจะเห็นว่า:

ts = 120 ns, td = 25 ns, tr = 13 ns, tf = 12 ns

ซึ่งหมายถึง t (on) = tr + td = 13 ns + 25 ns = 38 ns

t (ปิด) = ts + tf = 120 ns + 12 ns = 132 ns

ก่อนหน้านี้: วิธีการสร้าง PCB ที่บ้าน ถัดไป: วงจรซีเนอร์ไดโอดลักษณะการคำนวณ