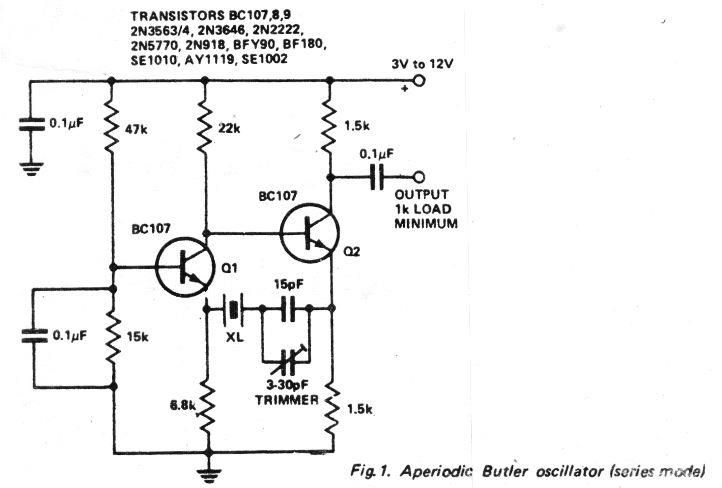

การกำหนดค่าที่ทรานซิสเตอร์แยกขั้วสองขั้วหรือ BJT เสริมด้วยตัวต้านทานอีซีแอลเพื่อเพิ่มเสถียรภาพในเรื่องการเปลี่ยนแปลงอุณหภูมิโดยรอบเรียกว่าวงจรไบแอสที่เสถียรของตัวปล่อยสำหรับ BJT

เราได้ศึกษาแล้วว่าคืออะไร การให้น้ำหนัก DC ในทรานซิสเตอร์ ตอนนี้เรามาเรียนรู้วิธีใช้ตัวต้านทานอีซีแอลเพื่อปรับปรุงเสถียรภาพของเครือข่ายไบแอส BJT DC

การใช้ Emitter Stabilized Bias Circuit

การรวมตัวต้านทานอีซีแอลเข้ากับไบแอส dc ของ BJT ทำให้มีเสถียรภาพที่เหนือกว่าหมายความว่ากระแสและแรงดันไฟฟ้าของ dc bias ยังคงใกล้เคียงกับที่ที่วงจรได้รับการแก้ไขโดยพิจารณาจากพารามิเตอร์ภายนอกเช่นการเปลี่ยนแปลงของอุณหภูมิและ ทรานซิสเตอร์เบต้า (กำไร)

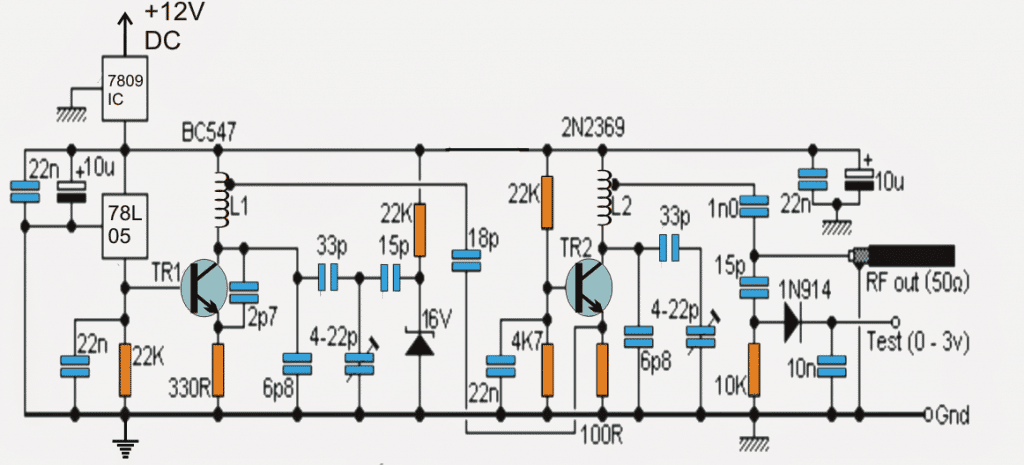

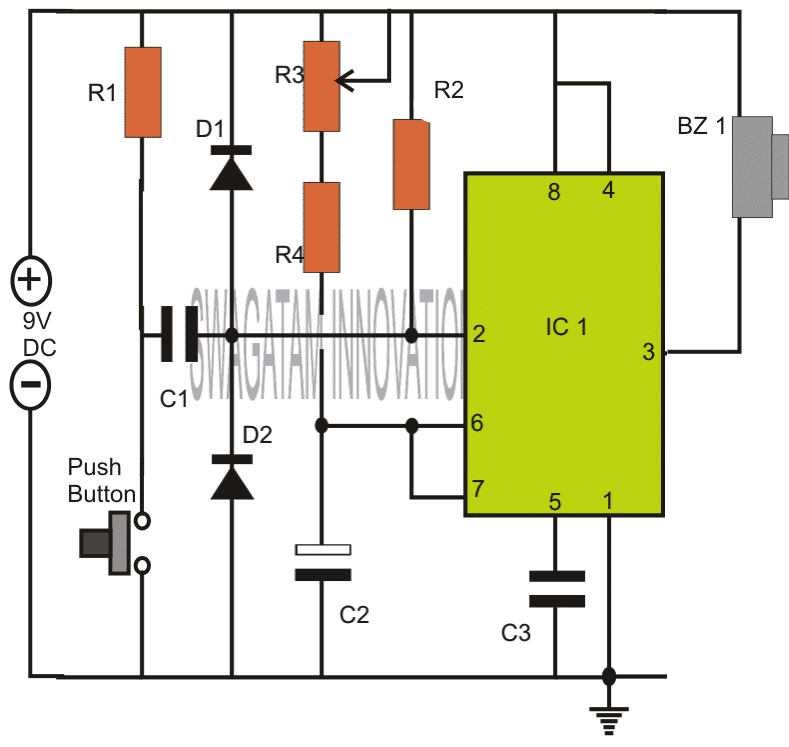

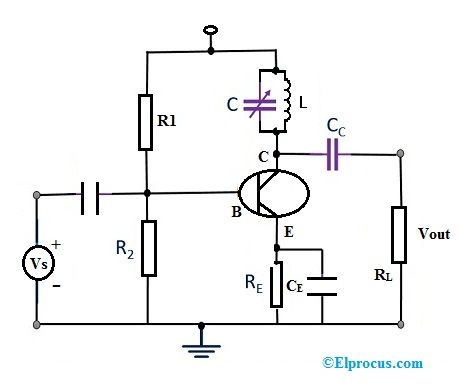

รูปที่ระบุด้านล่างแสดงเครือข่ายไบแอสของทรานซิสเตอร์ DC ที่มีตัวต้านทานอีซีแอลสำหรับบังคับใช้การให้น้ำหนักที่เสถียรของตัวปล่อยในการกำหนดค่าไบแอสคงที่ที่มีอยู่ของ BJT

รูปที่ 4.17 วงจรไบแอส BJT พร้อมตัวต้านทานอิมิตเตอร์

ในการอภิปรายของเราเราจะเริ่มการวิเคราะห์การออกแบบของเราโดยการตรวจสอบลูปรอบบริเวณตัวปล่อยฐานของวงจรก่อนจากนั้นใช้ผลลัพธ์เพื่อตรวจสอบลูปรอบด้านตัวรวบรวม - ตัวปล่อยของวงจรเพิ่มเติม

Base-Emitter Loop

เราสามารถวาดลูปตัวปล่อยฐานด้านบนใหม่ได้ตามวิธีที่แสดงด้านล่างในรูปที่ 4.18 และถ้าเรานำไปใช้ กฎแรงดันไฟฟ้าของ Kirchhoff บนลูปนี้ในทิศทางตามเข็มนาฬิกาช่วยให้เราได้สมการต่อไปนี้:

+ Vcc = IBRB - VBE - IERE = 0 ------- (4.15)

จากการสนทนาครั้งก่อนเราทราบว่า: IE = (β + 1) ข ------- (4.16)

การแทนค่าของ IE ใน Eq (4.15) ให้ผลลัพธ์ดังต่อไปนี้:

Vcc = IBRB - VBE - (β + 1) IBRE = 0

การใส่คำศัพท์ในกลุ่มที่เกี่ยวข้องให้ผลดังต่อไปนี้:

หากคุณจำได้จากบทก่อนหน้าของเราสมการอคติคงที่ได้มาในรูปแบบต่อไปนี้:

หากเราเปรียบเทียบสมการอคติคงที่นี้กับสมการ (4.17) เราจะพบความแตกต่างเพียงอย่างเดียวระหว่างสมการสองสมการสำหรับ IB ปัจจุบันคือคำว่า (β + 1) RE.

เมื่อใช้สมการ 4.17 ในการวาดโครงร่างตามอนุกรมเราสามารถดึงผลลัพธ์ที่น่าสนใจออกมาได้ซึ่งจริงๆแล้วก็คล้ายกับสมการ 4.17

ยกตัวอย่างเครือข่ายต่อไปนี้ในรูปที่ 4.19:

ถ้าเราแก้ระบบสำหรับ IB ปัจจุบันผลลัพธ์ในสมการเดียวกันที่ได้รับใน Eq 4.17. สังเกตว่านอกจากแรงดันไฟฟ้าจากฐานไปยังตัวปล่อย VBE แล้วตัวต้านทาน RE จะปรากฏขึ้นอีกครั้งที่อินพุตของวงจรฐานตามระดับ (β + 1)

ความหมายตัวต้านทานตัวปล่อยซึ่งเป็นส่วนหนึ่งของลูปตัวรวบรวม - ตัวปล่อยจะแสดงเป็น (β + 1) RE ในลูปตัวปล่อยฐาน

สมมติว่าβส่วนใหญ่อาจสูงกว่า 50 สำหรับ BJT ส่วนใหญ่ตัวต้านทานที่ตัวปล่อยของทรานซิสเตอร์อาจมีขนาดใหญ่กว่ามากในวงจรฐาน ดังนั้นเราจึงสามารถหาสมการทั่วไปต่อไปนี้สำหรับรูปที่ 4.20:

Ri = (β + 1) RE ------ (4.18)

คุณจะพบว่าสมการนี้มีประโยชน์มากในขณะที่แก้ปัญหาเครือข่ายในอนาคตมากมาย จริงๆแล้วสมการนี้ช่วยให้จำสมการ 4.17 ได้ง่ายขึ้น

ตามกฎของโอห์มเรารู้ว่ากระแสไฟฟ้าผ่านเครือข่ายคือแรงดันไฟฟ้าหารด้วยความต้านทานของวงจร

แรงดันไฟฟ้าสำหรับการออกแบบตัวปล่อยฐานคือ = Vcc - VBE

ความต้านทานที่เห็นใน 4.17 คือ RB + RE ซึ่งสะท้อนให้เห็นว่า (β + 1), และผลลัพธ์ก็คือสิ่งที่เรามีใน Eq 4.17

Collector – Emitter Loop

รูปด้านบนแสดงลูปตัวเก็บรวบรวม - ใช้ กฎหมายของ Kirchhoff ไปยังวงที่ระบุในทิศทางตามเข็มนาฬิกาเราจะได้สมการต่อไปนี้:

+ YESTERDAY + คุณคือ + ICRC - VCC = 0

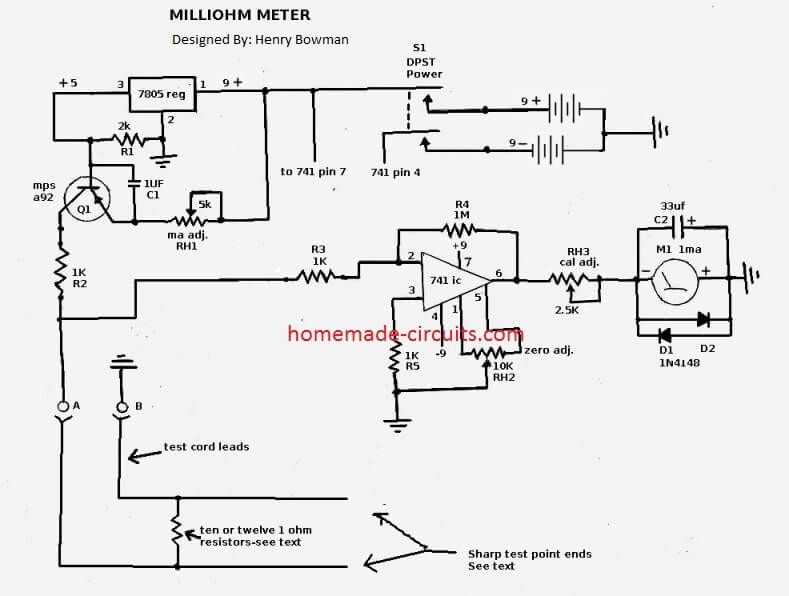

การแก้ตัวอย่างที่ใช้งานได้จริงสำหรับวงจรอคติที่มีเสถียรภาพของตัวปล่อยดังที่ระบุด้านล่าง:

สำหรับเครือข่ายอคติตัวปล่อยตามที่ระบุในรูปด้านบน 4.22 ให้ประเมินสิ่งต่อไปนี้:

- IB

- เข้าใจแล้ว

- คุณคือ

- ยู

- และ

- ฯลฯ

- VBC

การกำหนดระดับความอิ่มตัว

กระแสสะสมสูงสุดซึ่งกลายเป็นตัวเก็บรวบรวม ระดับความอิ่มตัว สำหรับเครือข่ายอิมิตเตอร์ไบแอสสามารถคำนวณได้โดยใช้กลยุทธ์ที่เหมือนกันซึ่งใช้กับเราก่อนหน้านี้ วงจรอคติคงที่ .

อาจใช้งานได้โดยการสร้างไฟฟ้าลัดวงจรข้ามตัวเก็บรวบรวมและตัวปล่อยนำของ BJT ตามที่ระบุไว้ในแผนภาพด้านบน 4.23 จากนั้นเราสามารถประเมินกระแสไฟฟ้าที่เป็นผลลัพธ์โดยใช้สูตรต่อไปนี้:

ตัวอย่างปัญหาสำหรับการแก้ปัญหาความอิ่มตัวของกระแสในวงจร BJT ที่เสถียรของตัวปล่อย:

โหลดการวิเคราะห์บรรทัด

การวิเคราะห์โหลดไลน์ของวงจร BJT ตัวปล่อยไบแอสค่อนข้างคล้ายกับการกำหนดค่าอคติคงที่ที่เรากล่าวถึงก่อนหน้านี้

ความแตกต่างเพียงอย่างเดียวคือระดับของ IB [ตามที่ได้มาจาก Eq ของเรา (4.17)] กำหนดระดับของ IB ตามลักษณะดังที่แสดงในรูปต่อไปนี้ 4.24 (ระบุว่าเป็น IBQ)

ก่อนหน้านี้: การวิเคราะห์โหลดไลน์ในวงจร BJT ถัดไป: แรงดันไฟฟ้าตัวแบ่งอคติในวงจร BJT - มีเสถียรภาพมากขึ้นโดยไม่มีปัจจัยเบต้า