มียุคหนึ่งที่คอมพิวเตอร์มีขนาดมหึมาขนาดที่จะติดตั้งได้ต้องใช้พื้นที่ห้องอย่างง่ายดาย แต่ปัจจุบันมีการพัฒนาจนเราสามารถพกพาเป็นโน้ตบุ๊กได้อย่างง่ายดาย นวัตกรรมที่ทำให้สิ่งนี้เป็นไปได้คือแนวคิดของวงจรรวม ใน วงจรรวม จำนวนมากที่ใช้งานอยู่และ องค์ประกอบแฝง พร้อมกับการเชื่อมต่อระหว่างกันของพวกเขาได้รับการพัฒนาบนเวเฟอร์ซิลิกอนขนาดเล็กโดยทั่วไปมีขนาด 50 x 50 ล้านในหน้าตัด กระบวนการพื้นฐานที่ตามมาสำหรับการผลิตวงจรดังกล่าว ได้แก่ การเจริญเติบโตแบบ epitaxial การแพร่กระจายของสิ่งเจือปนที่ปิดบังการเติบโตของออกไซด์และการกัดออกไซด์โดยใช้โฟโตลิโทกราฟีในการสร้างรูปแบบ

ส่วนประกอบของเวเฟอร์ ได้แก่ ตัวต้านทานทรานซิสเตอร์ไดโอดตัวเก็บประจุและอื่น ๆ องค์ประกอบที่ซับซ้อนที่สุดในการผลิตผ่าน IC คือทรานซิสเตอร์ ทรานซิสเตอร์มีหลายประเภท เช่น CMOS, BJT, FET เราเลือกประเภทของเทคโนโลยีทรานซิสเตอร์ที่จะนำมาใช้กับ IC ตามข้อกำหนด ในบทความนี้ให้เราทำความคุ้นเคยกับแนวคิดของ การผลิต CMOS (หรือ) การประดิษฐ์ทรานซิสเตอร์เป็น CMOS

การผลิต CMOS

สำหรับความต้องการในการกระจายพลังงานที่น้อยลง เทคโนโลยี CMOS ใช้สำหรับการติดตั้งทรานซิสเตอร์ หากเราต้องการวงจรที่เร็วกว่านั้นทรานซิสเตอร์จะถูกนำมาใช้ IC โดยใช้ BJT . การประดิษฐ์ของ ทรานซิสเตอร์ CMOS เนื่องจาก IC สามารถทำได้สามวิธี

เทคโนโลยี N-well / P-well ซึ่งการแพร่กระจายแบบ n จะกระทำบนพื้นผิวประเภท p หรือการแพร่กระจายแบบ p จะกระทำบนพื้นผิวชนิด n ตามลำดับ

เทคโนโลยี Twin well , ที่ไหน NMOS และทรานซิสเตอร์ PMOS ได้รับการพัฒนาบนเวเฟอร์โดยการแพร่กระจายพร้อมกันบนฐานการเจริญเติบโตแบบ epitaxial แทนที่จะเป็นสารตั้งต้น

กระบวนการซิลิกอนบนฉนวนซึ่งแทนที่จะใช้ซิลิกอนเป็นวัสดุพิมพ์จะใช้วัสดุฉนวนเพื่อเพิ่มความเร็วและความไวในการล็อค

เทคโนโลยี N-well / P- well

CMOS สามารถหาได้โดยการรวมทั้งสองอย่างเข้าด้วยกัน ทรานซิสเตอร์ NMOS และ PMOS มากกว่าเวเฟอร์ซิลิกอนเดียวกัน ในเทคโนโลยี N – well จะมีการกระจายหลุมชนิด n บนพื้นผิวชนิด p ในขณะที่หลุม P-type เป็นแบบรอง

ขั้นตอนการผลิต CMOS

กระบวนการผลิต CMOS ไหล ดำเนินการโดยใช้ขั้นตอนการประดิษฐ์ขั้นพื้นฐานยี่สิบขั้นตอนในขณะที่ผลิตโดยใช้เทคโนโลยี N-well / P-well

การสร้าง CMOS โดยใช้ N well

ขั้นตอนที่ 1: อันดับแรกเราเลือกวัสดุพิมพ์เป็นฐานสำหรับการประดิษฐ์ สำหรับหลุม N จะเลือกพื้นผิวซิลิกอนชนิด P

พื้นผิว

ขั้นตอนที่ 2 - ออกซิเดชั่น: การแพร่กระจายแบบเลือกของสิ่งสกปรกชนิด n สามารถทำได้โดยใช้ SiO2 เป็นตัวกั้นซึ่งช่วยปกป้องบางส่วนของเวเฟอร์จากการปนเปื้อนของสารตั้งต้น SiOสองถูกจัดวางโดยกระบวนการออกซิเดชั่นโดยให้สารตั้งต้นสัมผัสกับออกซิเจนและไฮโดรเจนคุณภาพสูงในห้องออกซิเดชั่นที่อุณหภูมิประมาณ 1,0000ค

ออกซิเดชัน

ขั้นตอนที่ 3 - การเติบโตของช่างภาพ: ในขั้นตอนนี้เพื่ออนุญาตการแกะสลักแบบเลือกชั้น SiO2 จะอยู่ภายใต้กระบวนการโฟโตลิโทกราฟี ในกระบวนการนี้เวเฟอร์จะถูกเคลือบด้วยฟิล์มที่สม่ำเสมอของอิมัลชันไวแสง

การเติบโตของ Photoresist

ขั้นตอนที่ 4 - การกำบัง: ขั้นตอนนี้เป็นความต่อเนื่องของกระบวนการโฟโตลิโทกราฟี ในขั้นตอนนี้รูปแบบการเปิดกว้างที่ต้องการจะทำโดยใช้ลายฉลุ ลายฉลุนี้ใช้เป็นหน้ากากเหนือช่างภาพ วัสดุพิมพ์ถูกสัมผัสกับ รังสียูวี photoresist ที่อยู่ภายใต้บริเวณที่สัมผัสกับหน้ากากจะได้รับโพลีเมอไรเซชัน

การปิดบัง Photoresist

ขั้นตอนที่ 5 - การลบ Photoresist ที่ไม่ได้รับแสง: หน้ากากจะถูกถอดออกและบริเวณที่ไม่ได้สัมผัสของโฟโตรีซิสต์จะละลายโดยการพัฒนาเวเฟอร์โดยใช้สารเคมีเช่นไตรคลอโรเอทิลีน

การกำจัด Photoresist

ขั้นตอนที่ 6 - การแกะสลัก: เวเฟอร์ถูกแช่อยู่ในสารละลายกัดกรดไฮโดรฟลูออริกซึ่งจะกำจัดออกไซด์ออกจากบริเวณที่จะนำสารเจือปน

การแกะสลัก SiO2

ขั้นตอนที่ 7 - การลบเลเยอร์ Photoresist ทั้งหมด: ในช่วง กระบวนการแกะสลัก ส่วนของ SiO2 ที่ได้รับการปกป้องโดยชั้นโฟโตเรสต์จะไม่ได้รับผลกระทบ ตอนนี้หน้ากากโฟโตเรสต์ถูกถอดออกด้วยตัวทำละลายเคมี (H2SO4 ร้อน)

การกำจัด Photoresist Layer

ขั้นตอนที่ 8 - การก่อตัวของหลุม N: สิ่งสกปรกประเภท n จะแพร่กระจายไปยังสารตั้งต้นชนิด p ผ่านบริเวณที่สัมผัสจึงก่อตัวเป็นหลุม N

การก่อตัวของ N-well

ขั้นตอนที่ 9 - การลบ SiO2: ตอนนี้ชั้นของ SiO2 ถูกกำจัดออกโดยใช้กรดไฮโดรฟลูออริก

การกำจัด SiO2

ขั้นตอนที่ 10 - การสะสมของโพลีซิลิคอน: การวางแนวของประตูก ทรานซิสเตอร์ CMOS จะนำไปสู่ความจุที่ไม่ต้องการซึ่งอาจเป็นอันตรายต่อวงจร ดังนั้นเพื่อป้องกันไม่ให้ 'กระบวนการประตูปรับแนวด้วยตัวเอง' นี้จึงเป็นที่ต้องการสำหรับบริเวณประตูก่อนการสร้างแหล่งที่มาและการระบายโดยใช้การฝังไอออน

การสะสมของโพลีซิลิคอน

โพลีซิลิคอนใช้ในการก่อตัวของประตูเนื่องจากสามารถทนต่ออุณหภูมิสูงได้มากกว่า 80000c เมื่อเวเฟอร์ต้องผ่านกรรมวิธีการหลอมเพื่อสร้างแหล่งที่มาและท่อระบายน้ำ โพลีซิลิคอนถูกสะสมโดยใช้ กระบวนการสะสมทางเคมี เหนือชั้นบาง ๆ ของเกตออกไซด์ เกตออกไซด์บาง ๆ นี้ภายใต้ชั้นโพลีซิลิคอนช่วยป้องกันไม่ให้สารเจือปนใต้บริเวณประตู

ขั้นตอนที่ 11 - การก่อตัวของเขตประตู: ยกเว้นสองภูมิภาคที่จำเป็นสำหรับการสร้างประตูสำหรับ ทรานซิสเตอร์ NMOS และ PMOS ส่วนที่เหลือของ Polysilicon จะถูกลอกออก

การก่อตัวของเขตประตู

ขั้นตอนที่ 12 - กระบวนการออกซิเดชั่น: ชั้นออกซิเดชั่นจะถูกทับถมบนเวเฟอร์ซึ่งทำหน้าที่เป็นเกราะป้องกันต่อไป กระบวนการแพร่กระจายและการทำให้เป็นโลหะ .

กระบวนการออกซิเดชั่น

ขั้นตอนที่ 13 - การกำบังและการแพร่กระจาย: สำหรับการสร้างพื้นที่สำหรับการแพร่กระจายของสิ่งสกปรกประเภท n โดยใช้กระบวนการกำบังช่องว่างขนาดเล็กจะทำ

กำบัง

การใช้กระบวนการแพร่กระจายพื้นที่ n + สามแห่งได้รับการพัฒนาสำหรับการสร้างขั้วของ NMOS

N- การแพร่กระจาย

ขั้นตอนที่ 14 - การกำจัดออกไซด์: ชั้นออกไซด์ถูกลอกออก

การกำจัดออกไซด์

ขั้นตอนที่ 15 - การแพร่กระจายแบบ P: คล้ายกับการแพร่กระจายแบบ n สำหรับการสร้างขั้วของการแพร่กระจายของ PMOS p-type จะดำเนินการ

P-Type แพร่

ขั้นตอนที่ 16 - การวางออกไซด์ของสนามหนา: ก่อนที่จะขึ้นรูปขั้วโลหะจะมีการวางออกไซด์ของฟิลด์หนาเพื่อสร้างชั้นป้องกันสำหรับบริเวณของเวเฟอร์ที่ไม่จำเป็นต้องใช้ขั้วใด

ชั้นออกไซด์หนา

ขั้นตอนที่ 17 - การทำให้เป็นโลหะ: ขั้นตอนนี้ใช้สำหรับการก่อตัวของขั้วโลหะซึ่งสามารถให้การเชื่อมต่อระหว่างกัน อลูมิเนียมกระจายอยู่บนแผ่นเวเฟอร์ทั้งหมด

การทำให้เป็นโลหะ

ขั้นตอนที่ 18 - การกำจัดโลหะส่วนเกิน: โลหะส่วนเกินจะถูกนำออกจากเวเฟอร์

ขั้นตอนที่ 19 - การสร้างขั้ว: ในช่องว่างที่เกิดขึ้นหลังจากการกำจัดขั้วโลหะส่วนเกินจะเกิดขึ้นสำหรับการเชื่อมต่อระหว่างกัน

การก่อตัวของขั้ว

ขั้นตอนที่ 20 - การกำหนดชื่อเทอร์มินัล: ชื่อถูกกำหนดให้กับเทอร์มินัลของ ทรานซิสเตอร์ NMOS และ PMOS .

การกำหนดชื่อ Terminal

การสร้าง CMOS โดยใช้เทคโนโลยี P well

กระบวนการ p-well นั้นคล้ายกับกระบวนการ N well ยกเว้นว่าที่นี่ใช้วัสดุพิมพ์ชนิด n และทำการแพร่กระจายชนิด p เพื่อความเรียบง่ายโดยทั่วไปควรใช้กระบวนการ N well

การผลิตท่อคู่ของ CMOS

การใช้กระบวนการ Twin-tube สามารถควบคุมการขยายของอุปกรณ์ประเภท P และ N ได้ ขั้นตอนต่างๆที่เกี่ยวข้องใน การผลิต CMOS โดยใช้วิธี Twin-tube มีรายละเอียดดังนี้

- ใช้วัสดุพิมพ์ชนิด n หรือ p ที่เจือเล็กน้อยและใช้ชั้น epitaxial ชั้น Epitaxial ช่วยป้องกันปัญหาการสลักในชิป

- ชั้นซิลิกอนที่มีความบริสุทธิ์สูงที่มีความหนาที่วัดได้และมีความเข้มข้นของสารเจือปนที่แน่นอน

- การก่อตัวของท่อสำหรับหลุม P และ N

- โครงสร้างออกไซด์บาง ๆ เพื่อป้องกันการปนเปื้อนในระหว่างกระบวนการแพร่กระจาย

- แหล่งที่มาและท่อระบายน้ำเกิดขึ้นโดยใช้วิธีการฝังไอออน

- มีดตัดสำหรับทำบางส่วนสำหรับหน้าสัมผัสโลหะ

- Metallization ทำเพื่อวาดหน้าสัมผัสโลหะ

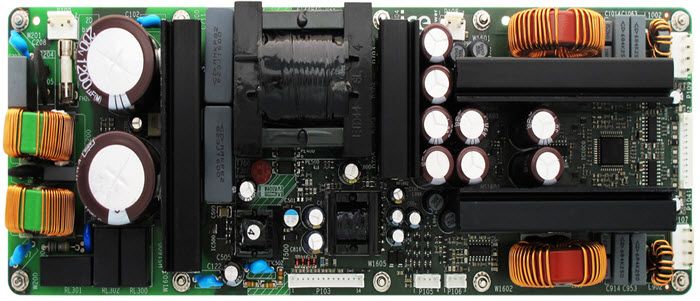

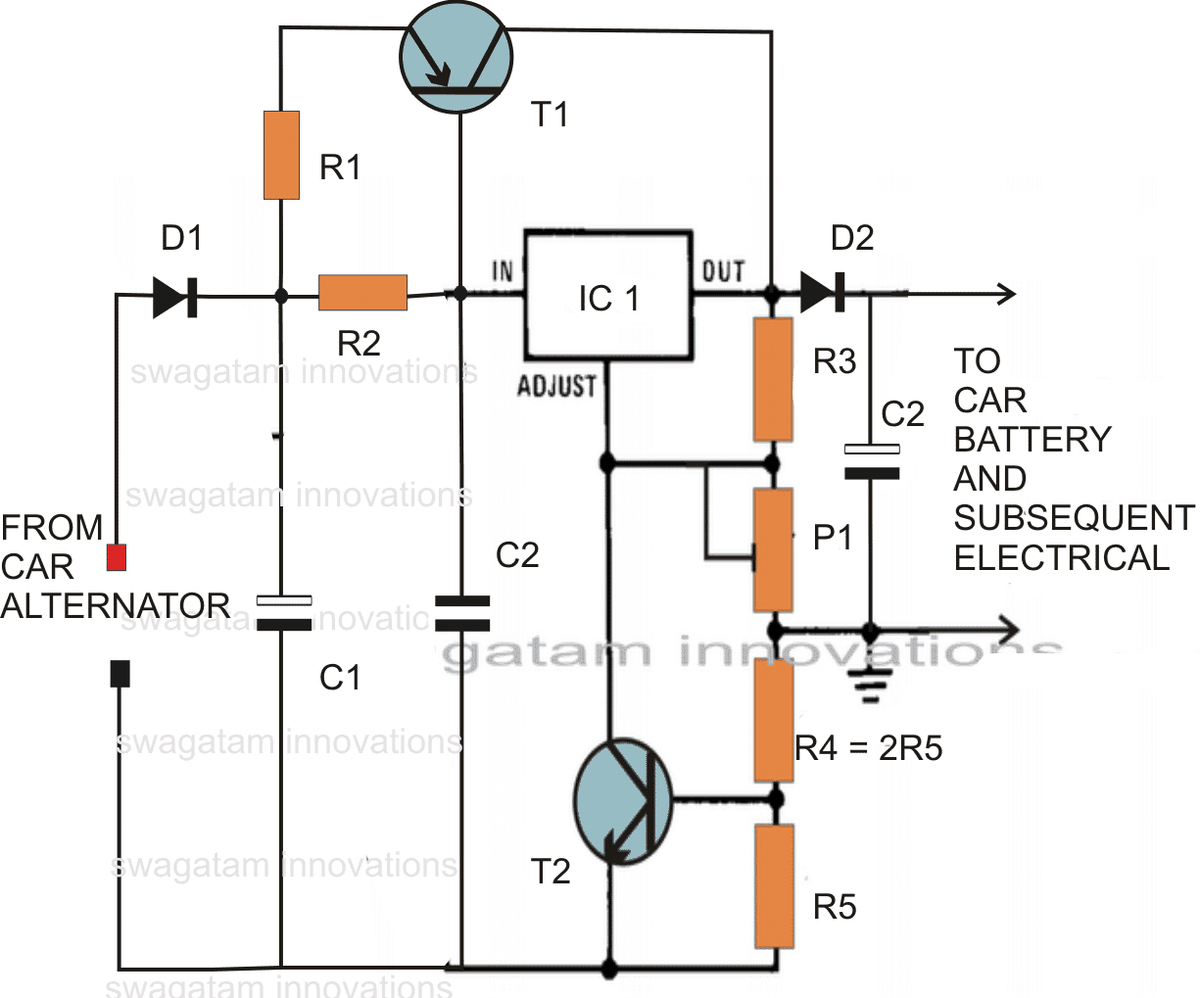

เค้าโครง CMOS IC

มุมมองด้านบนของ เป็น CMOS การประดิษฐ์และการจัดวาง ได้รับ ที่นี่สามารถดูหน้าสัมผัสโลหะต่างๆและการกระจายตัวของ N ได้อย่างชัดเจน

เค้าโครง CMOS IC

ดังนั้นทั้งหมดนี้เป็นข้อมูลเกี่ยวกับ เทคนิคการประดิษฐ์ CMOS . ให้เราพิจารณาเวเฟอร์ขนาด 1 นิ้วที่แบ่งออกเป็น 400 ชิปของพื้นที่ผิว 50 ล้านคูณ 50 มิล ใช้พื้นที่ 50 ล้าน 2 ในการประดิษฐ์ทรานซิสเตอร์ ดังนั้น IC แต่ละตัวจึงมีทรานซิสเตอร์ 2 ตัวจึงมีทรานซิสเตอร์ 2 x 400 = 800 ที่สร้างขึ้นบนเวเฟอร์แต่ละตัว หากมีการประมวลผลเวเฟอร์ 10 ตัวในแต่ละชุดจะสามารถผลิตทรานซิสเตอร์ 8000 พร้อมกันได้ คุณสังเกตเห็นส่วนประกอบต่างๆบน IC อย่างไร?