IC 4040 เป็นชิปตัวนับระลอกไบนารี 12 ขั้นตอนในทางเทคนิคกล่าวง่ายๆคืออุปกรณ์ที่จะสร้างเอาต์พุตความถี่ล่าช้าที่คำนวณได้เพื่อตอบสนองทุกพัลส์ที่ใช้ที่อินพุตนาฬิกา ความล่าช้านี้จะเพิ่มขึ้นที่อัตรา 2 ^ (n) โดยที่ n คือลำดับพินเอาต์ในลำดับของเอาต์พุต

ข้อกำหนดทางเทคนิคหลัก

คุณสมบัติหลักและข้อมูลจำเพาะของ IC อาจเข้าใจได้ดังนี้:

บัฟเฟอร์เต็ม 12 เอาต์พุตซึ่งแบ่งนาฬิกาอินพุตที่อัตรา 2 ^ (n) โดยที่ n = ลำดับพินเอาต์เริ่มตั้งแต่ Q0 จนถึง Q11

การเรียงลำดับเอาต์พุตข้างต้นเกิดขึ้นเพื่อตอบสนองทุกขอบนาฬิกาที่ลดลงที่ใช้กับอินพุต CP pinout ของนาฬิกา IC จะตอบสนองแม้กระทั่งชีพจรนาฬิกาที่ลดลงค่อนข้างช้าอย่างมีประสิทธิภาพ

อินพุตรีเซ็ตต้นแบบอะซิงโครนัส (MR) แบบอะซิงโครนัสเดียวซึ่งรีเซ็ตเอาต์พุตทั้งหมดเป็นศูนย์เมื่อใช้ลอจิกสูงในขณะที่ตรรกะต่ำคงที่ทำให้ IC ยังคงทำงานอยู่

IC จะทำงานได้เต็มที่ด้วย Vdd ที่ต่ำถึง 3V และรักษาลักษณะการทำงานคงที่แม้ที่แรงดันไฟฟ้าประมาณ 15V

ลองตรวจสอบพารามิเตอร์ที่ไม่ควรเกินสำหรับ IC 4040

- แรงดันไฟฟ้า (Vdd) = โดยทั่วไประหว่าง 3V ถึง 15V, 18V เป็นขีด จำกัด สูงสุด

- แรงดันไฟฟ้าขาเข้า (Vi) = แรงดันไฟฟ้าที่อาจใช้กับอินพุตเช่น CP, MR เป็นต้นโดยทั่วไปควรต่ำกว่า Vdd หรือมากที่สุด = Vdd + 0.5V

- ความต้องการกระแสไฟฟ้าในการทำงานที่เหมาะสมที่สุด = 50mA เนื่องจากมีเอาต์พุตจำนวนมากและแต่ละเอาต์พุต

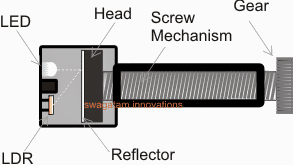

รายละเอียด Pinout

แผนภาพด้านบนแสดงถึงการกำหนดค่าพินเอาต์ของ IC 4040 ซึ่งอาจได้รับการประเมินตามที่ระบุไว้ใน:

Pinouts Q0 ถึง Q11 เป็นเอาต์พุตของ IC

- Vss คือพินกราวด์

- Vdd คือพินบวก

- MR คือหมุดรีเซ็ต

- CP คืออินพุตนาฬิกา

ลำดับเวลา

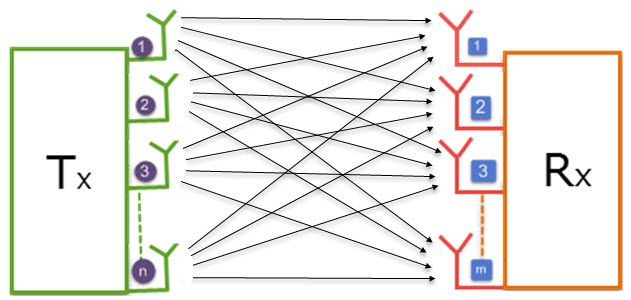

ตอนนี้เรามาวิเคราะห์ลำดับเวลาเอาต์พุตของ IC 4040 ดังแสดงในแผนภาพต่อไปนี้เราสามารถดูและเข้าใจรายละเอียดต่อไปนี้:

ตราบใดที่อินพุต MR สูงเอาต์พุต IC จะไม่ตอบสนอง ทันทีที่ค่าต่ำ IC จะเริ่มตอบสนองและนับนาฬิกาอินพุตที่อินพุต CP

ขาเอาต์พุตแรก Q0 จะสูงหลังจาก 2 ^ (n) นาฬิกาที่ CP นั่นคือ = 2 ^ (0) = 1 ซึ่งหมายความว่า Q0 จะสูงที่ขอบด้านล่างของพัลส์แรกและไปต่ำเพื่อตอบสนองต่อขอบที่ตกลงมาของ นาฬิกาที่ตามมาและอื่น ๆ

ในทำนองเดียวกัน Q1 จะสูงหลังจาก 2 ^ (1) = 2 ซึ่งหมายความว่ามันจะสูงทันทีที่ตรวจพบขอบที่ตกลงมาของนาฬิกาที่สองและไปต่ำที่ขอบตกของนาฬิกาที่ 4 ตามมาเป็นต้น

ในทำนองเดียวกัน Q2 จะสูงและต่ำหลังจาก 2 ^ (2) = ขอบตกของนาฬิกาที่ 4 และอื่น ๆ

ลำดับข้างต้นจะดำเนินต่อไปจนถึง Q11 เพื่อตอบสนองต่ออินพุตนาฬิกาที่คงที่ที่ CP

หมายความว่าถ้าสมมติว่า CP ถูกโอเวอร์คล็อกด้วยพัลส์ 1Hz Q11 จะสูงขึ้นหลังจาก 2 ^ 11 วินาทีหรือหลังจาก 2048 วินาทีซึ่งเท่ากับ 34 นาทีโดยประมาณลองนึกภาพช่วงของการหน่วงเวลาที่คุณสามารถทำได้โดยเพียงแค่เพิ่มอินพุตนาฬิกาโดย วินาทีหรืออาจเป็นนาที

คำแนะนำการใช้งาน

จากการวิเคราะห์โดยละเอียดข้างต้นของแผ่นข้อมูล IC 4040 เราสามารถสรุปได้ว่าโดยทั่วไปแล้ว IC จะเหมาะสำหรับการใช้งานทั้งหมดที่เกี่ยวข้องกับข้อกำหนดการแบ่งความถี่หรือข้อกำหนดการสร้างช่วงเวลาที่ล่าช้า

ดังนั้นจึงเหมาะอย่างยิ่งสำหรับการใช้งานวงจรแบ่งความถี่ตัวจับเวลาระยะยาวไฟแฟลชและการใช้งานอื่น ๆ ที่คล้ายคลึงกัน

ก่อนหน้านี้: การใช้ฮีทซิงค์แบบรางอลูมิเนียมสำหรับไฟ LED สูงแทน PCB ถัดไป: วงจรตั้งเวลาปลุกมอเตอร์เครื่องซักผ้า