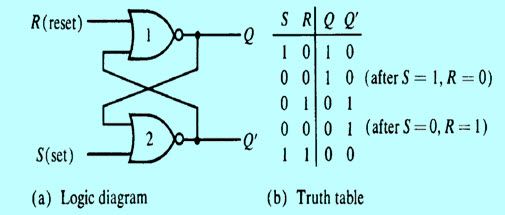

วงจรผสม อย่าใช้หน่วยความจำใด ๆ ดังนั้นตำแหน่งอินพุตก่อนหน้านี้จะไม่รวมผลลัพธ์ใด ๆ ในสถานการณ์ปัจจุบันของวงจร แม้ว่าวงจรตามลำดับจะมีหน่วยความจำดังนั้นเอาต์พุตจึงขึ้นอยู่กับอินพุตซึ่งหมายความว่าเอาต์พุตสามารถเปลี่ยนแปลงได้ตามอินพุต การทำงานของวงจรเหล่านี้สามารถทำได้โดยใช้อินพุตวงจรก่อนหน้า, CLK, หน่วยความจำและเอาต์พุต บทความนี้กล่าวถึงภาพรวมของฟลิปฟล็อปมาสเตอร์ทาส แต่ก่อนที่จะไปทำความรู้จักกับ Flip-Flop นี้เราต้องรู้เกี่ยวกับพื้นฐานของ รองเท้าแตะ เช่น SR flip flop และ JK flip flop

Master-Slave Flip Flop คืออะไร?

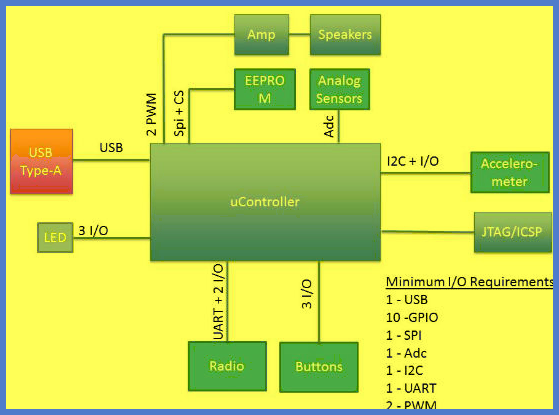

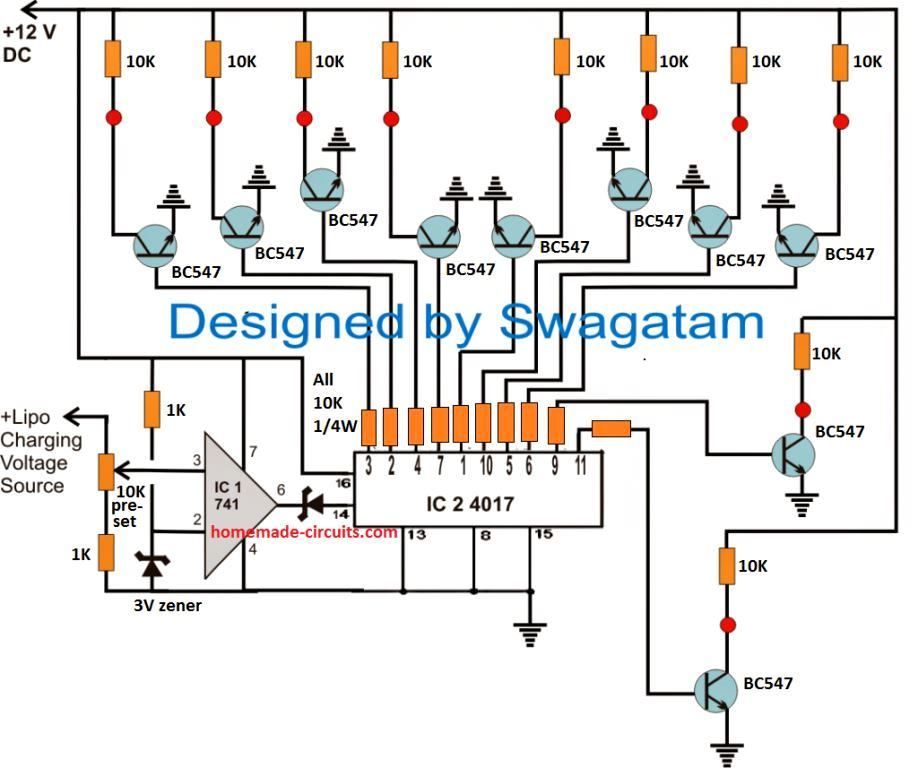

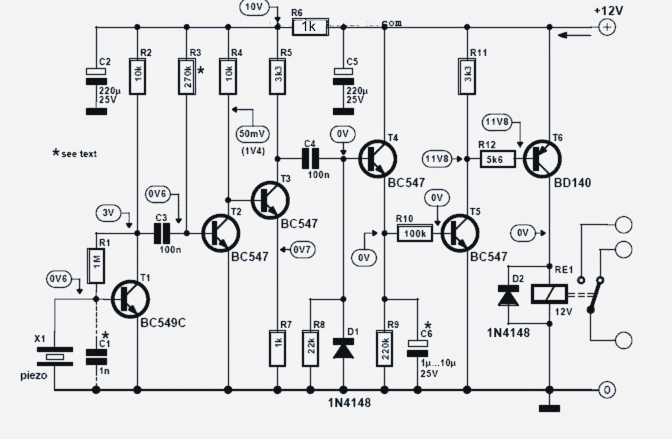

โดยพื้นฐานแล้วฟลิปฟล็อปประเภทนี้สามารถออกแบบให้มี JK FF สองตัวได้โดยการต่อแบบอนุกรม FF หนึ่งใน FF เหล่านี้ FF หนึ่งตัวทำงานเป็นมาสเตอร์และ FF อื่น ๆ ทำงานเหมือนทาส การเชื่อมต่อของ FF เหล่านี้สามารถทำได้เช่นนี้เอาต์พุต FF หลักสามารถเชื่อมต่อกับอินพุตของ FF Slave ที่นี่เอาต์พุตของ slave FF สามารถเชื่อมต่อกับอินพุตของ FF หลักได้

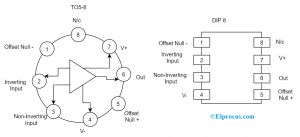

ใน FF ประเภทนี้ อินเวอร์เตอร์ นอกจากนี้ยังใช้นอกเหนือจาก FF สองตัว การเชื่อมต่ออินเวอร์เตอร์สามารถทำได้ในลักษณะที่พัลส์ CLK กลับด้านสามารถเชื่อมต่อกับทาส FF ได้ ในอีกแง่หนึ่งถ้า CLK pulse เป็น 0 สำหรับมาสเตอร์ FF พัลส์ CLK จะเป็น 1 สำหรับทาส FF ในทำนองเดียวกันเมื่อ CLK pulse เป็น 1 สำหรับ master FF ดังนั้น CLK pulse จะเป็น 0 สำหรับ slave FF

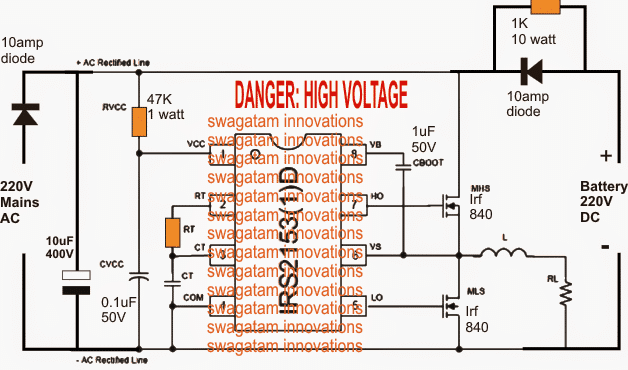

ต้นแบบทาสฟลิปฟล็อปวงจร

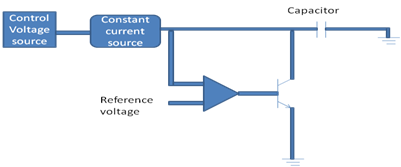

Master-Slave FF ทำงาน

เมื่อใดก็ตามที่พัลส์ CLK ไปสูงซึ่งหมายถึง 1 ทาสสามารถแยกอินพุตได้เช่น J & K อาจเปลี่ยนสภาพของระบบ

ทาส FF สามารถถูกถอดออกได้จนกว่าพัลส์ CLK จะไปต่ำซึ่งหมายถึง 0 เมื่อใดก็ตามที่พัลส์ CLK กลับสู่สถานะต่ำข้อมูลจะถูกส่งจาก FF ต้นแบบไปยังทาส FF และสุดท้าย o / p สามารถรับได้

ในตอนแรก FF หลักจะถูกเรียกที่ระดับบวกในขณะที่ FF ทาสจะถูกเรียกที่ระดับลบ ด้วยเหตุนี้ FF ต้นแบบจึงตอบสนองก่อน

ถ้า J = 0 & K = 1 ผลลัพธ์ของ FF 'Q' หลักจะไปที่อินพุต K ของทาส FF และ CLK บังคับให้ทาส FF เป็น RST (รีเซ็ต) ดังนั้นทาส FF จึงคัดลอก FF ต้นแบบ

ถ้า J = 1 & K = 0 ดังนั้น FF ‘Q’ หลักจะไปที่อินพุต J ของทาส FF และการเปลี่ยนค่าลบของ CLK จะตั้งค่าทาส FF และคัดลอกต้นแบบ

ถ้า J = 1 & K = 1 มันจะสลับไปที่การเปลี่ยนแปลงเชิงบวกของ CLK และทาสจะสลับไปที่การเปลี่ยนแปลงเชิงลบของ CLK

ถ้าทั้ง J & K เป็น 0 FF ก็จะถูกตรึงไว้และ Q จะไม่สามารถเคลื่อนย้ายได้

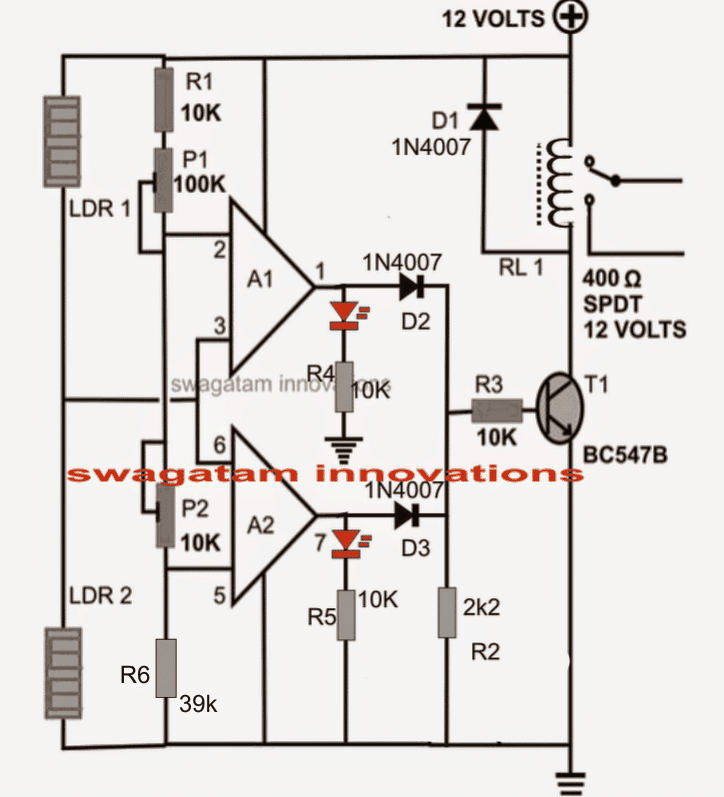

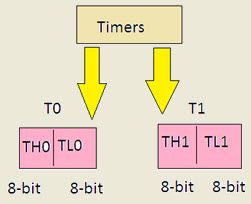

แผนภาพเวลา

- เมื่อทั้ง CLK พัลส์ & o / p ของมาสเตอร์สูงก็จะยังคงสูงจนกระทั่ง CLK อยู่ในระดับต่ำเนื่องจากสถานะถูกจัดเก็บ

- ในปัจจุบัน o / p ของมาสเตอร์เปลี่ยนเป็นระดับต่ำเมื่อพัลส์ CLK เปลี่ยนเป็นสูงอีกครั้งและยังคงต่ำจนกว่า CLK จะเปลี่ยนเป็นสูงอีกครั้ง

- ดังนั้นการสลับจึงเกิดขึ้นสำหรับวงจร CLK

ไทม์มิ่งไดอะแกรมของ a-master-slave-FF

- เมื่อใดก็ตามที่พัลส์ CLK เป็น 1 มาสเตอร์จะถูกตั้งค่า แต่ไม่ใช่ทาสดังนั้นทาส o / p จะยังคงเป็น '0' จนกว่า CLK จะยังคงเป็น 1

- เมื่อ CLK ต่ำทาสจะเปลี่ยนเป็นใช้งานได้และยังคงเป็น '1' จนกว่า CLK จะเปลี่ยนเป็น '0' อีกครั้ง

- การสลับจะเกิดขึ้นตลอดขั้นตอนทั้งหมดในขณะที่ o / p กำลังเปลี่ยนแปลงหนึ่งครั้งภายในหนึ่งรอบ

- สิ่งนี้ทำให้ฟลิปฟล็อปเป็นอุปกรณ์ซิงโครนัสเนื่องจากส่งผ่านข้อมูลด้วยเวลาสัญญาณ CLK เท่านั้น

ดังนั้นทั้งหมดนี้จึงเกี่ยวกับ Master-Slave รองเท้าแตะ . จากข้อมูลข้างต้นในที่สุดเราสามารถสรุปได้ว่า FF นี้สามารถสร้างขึ้นด้วย FF สองตัวคือ master และ slave เมื่อ FF ตัวหนึ่งทำหน้าที่เหมือนวงจรหลักมันจะเปิดใช้งานที่ขอบนำของพัลส์ CLK ในทำนองเดียวกันเมื่อ FF อีกตัวทำหน้าที่เหมือนวงจรทาสมันจะเปิดใช้งานบนขอบที่ตกลงมาของพัลส์ CLK