กระบวนการออกแบบฮาร์ดแวร์ดิจิทัลได้เปลี่ยนไปอย่างมากในช่วงไม่กี่ปีที่ผ่านมา ดังนั้นวงจรดิจิทัลขนาดเล็กจึงสามารถใช้งานได้โดยใช้ PAL และ PLA ใช้อุปกรณ์แต่ละชิ้น เพื่อใช้วงจรต่างๆ ที่ไม่ต้องการมากกว่าจำนวน i / ps, o / ps และข้อกำหนดผลิตภัณฑ์ที่มีให้ในชิปเฉพาะ ชิปเหล่านี้มีขนาดไม่เพียงพอกับขนาดที่ค่อนข้างเจียมเนื้อเจียมตัวโดยปกติจะรองรับจำนวนอินพุตและเอาต์พุตร่วมกันไม่เกิน 32 สำหรับการออกแบบวงจรเหล่านี้ที่ต้องการอินพุตและเอาต์พุตเพิ่มเติมคุณสามารถใช้ PLAs / PAL จำนวนมากหรือประเภทอื่นที่ดีกว่า ของชิปสามารถใช้เรียกว่า CPLD (อุปกรณ์ลอจิกที่ตั้งโปรแกรมได้ซับซ้อน) ชิป CPLD ประกอบด้วยบล็อกวงจรหลายตัวบนชิปตัวเดียวพร้อมทรัพยากรการเดินสายภายในเพื่อต่อบล็อกวงจร แต่ละวงจรเทียบได้กับ PLA หรือ PAL

อุปกรณ์ลอจิกที่ตั้งโปรแกรมได้ซับซ้อนคืออะไร?

คำย่อของ CPLD คือ 'อุปกรณ์ลอจิกที่ตั้งโปรแกรมได้ซับซ้อน' ซึ่งเป็นอุปกรณ์หนึ่ง ชนิดของวงจรรวม ที่นักออกแบบแอปพลิเคชันออกแบบมาเพื่อใช้ฮาร์ดแวร์ดิจิทัลเช่นโทรศัพท์มือถือ สิ่งเหล่านี้สามารถรองรับการออกแบบที่สูงกว่า SPLD (อุปกรณ์ตรรกะที่ตั้งโปรแกรมได้ง่าย ๆ ) แต่มีตรรกะน้อยกว่า FPGA ( อาร์เรย์ประตูที่ตั้งโปรแกรมได้ ) CPLD ประกอบด้วยบล็อกตรรกะจำนวนมากแต่ละบล็อกมีมาโครเซลล์ 8-16 ตัว เนื่องจากทุกบล็อกลอจิกเรียกใช้ฟังก์ชันเฉพาะ macrocells ทั้งหมดในบล็อกลอจิกจึงเชื่อมต่อกันอย่างสมบูรณ์ บล็อกเหล่านี้อาจเชื่อมต่อกันหรือไม่ก็ได้ทั้งนี้ขึ้นอยู่กับการใช้งาน

อุปกรณ์ลอจิกที่ตั้งโปรแกรมได้ซับซ้อน

CPLD ส่วนใหญ่ (อุปกรณ์ลอจิกที่ตั้งโปรแกรมได้ซับซ้อน) มีมาโครเซลล์ที่มีผลรวมของฟังก์ชันลอจิกและวิชาเลือก FF (ฟลิปฟล็อป) . ทั้งนี้ขึ้นอยู่กับชิปฟังก์ชันลอจิกคอมบิเนเตอร์รองรับตั้งแต่ 4 ถึง 16 เงื่อนไขของผลิตภัณฑ์พร้อมพัดลมอิน CPLD ยังแตกต่างกันในแง่ของการลงทะเบียนกะและลอจิกเกต ด้วยเหตุนี้ CPLD ที่มีลอจิกเกตจำนวนมากอาจถูกใช้แทน FPGA ข้อกำหนด CPLD อื่นหมายถึงจำนวนเงื่อนไขของผลิตภัณฑ์ที่ macrocell สามารถทำได้ เงื่อนไขของผลิตภัณฑ์คือผลผลิตของสัญญาณดิจิทัลที่เรียกใช้ฟังก์ชันลอจิกเฉพาะ

CPLD มีอยู่ในรูปแบบแพ็กเกจ IC และตระกูลตรรกะต่างๆ CPLD ยังแตกต่างกันในแง่ของแรงดันไฟฟ้ากระแสไฟฟ้ากระแสไฟสแตนด์บายและการกระจายพลังงาน นอกจากนี้ยังสามารถหาได้ด้วยหน่วยความจำจำนวนมากและการสนับสนุนหน่วยความจำประเภทต่างๆ โดยปกติหน่วยความจำจะแสดงเป็นบิต / เมกะบิต การสนับสนุนหน่วยความจำประกอบด้วย ROM, RAM และแรมสองพอร์ต นอกจากนี้ยังประกอบด้วย CAM (หน่วยความจำแอดเดรสเนื้อหา) เช่นเดียวกับหน่วยความจำ FIFO (เข้าก่อนออกก่อน) และหน่วยความจำ LIFO (เข้าก่อนสุดท้ายออก)

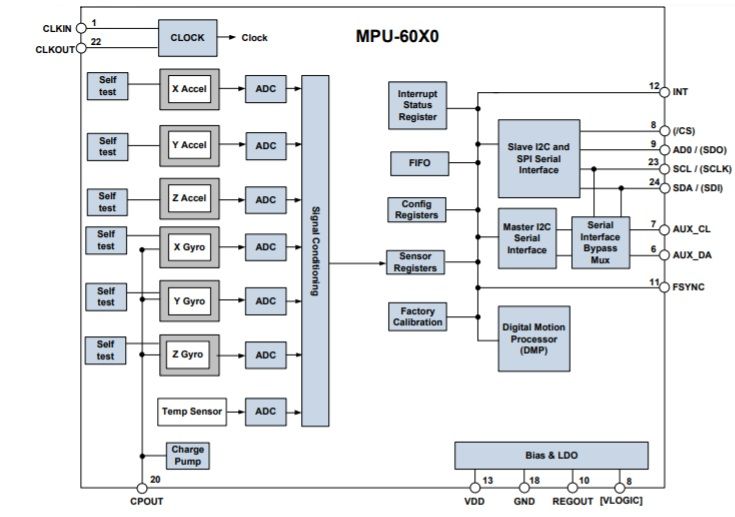

สถาปัตยกรรมของอุปกรณ์ลอจิกที่ตั้งโปรแกรมได้ซับซ้อน

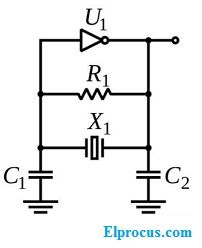

อุปกรณ์ลอจิกที่ตั้งโปรแกรมได้ซับซ้อนประกอบด้วยกลุ่ม FB ที่ตั้งโปรแกรมได้ (บล็อกการทำงาน) อินพุตและเอาต์พุตของบล็อกการทำงานเหล่านี้เชื่อมต่อกันด้วย GIM (เมทริกซ์การเชื่อมต่อโครงข่ายส่วนกลาง) เมทริกซ์การเชื่อมต่อโครงข่ายนี้สามารถกำหนดค่าใหม่ได้เพื่อให้เราสามารถปรับเปลี่ยนผู้ติดต่อระหว่างบล็อกการทำงานได้ จะมีบล็อกอินพุตและเอาต์พุตบางส่วนที่ให้เรารวม CPLD กับโลกภายนอก สถาปัตยกรรมของ CPLD แสดงไว้ด้านล่าง

โดยทั่วไป FB ที่ตั้งโปรแกรมได้จะดูเหมือนไฟล์ อาร์เรย์ของลอจิกเกต ซึ่งสามารถตั้งโปรแกรมอาร์เรย์ของ AND gate ได้และ OR gate มีความเสถียร แต่ผู้ผลิตแต่ละรายมีวิธีคิดในการออกแบบบล็อกการทำงาน o / p ในรายการสามารถพบได้โดยการใช้งานสัญญาณตอบรับที่ได้รับจากเอาต์พุต OR gate

สถาปัตยกรรม CPLD

ในการเขียนโปรแกรม CPLD การออกแบบจะถูกเข้ารหัสเป็นภาษา Verilog หรือ VHDL เป็นครั้งแรกเมื่อโค้ดถูก (จำลองและสังเคราะห์ในระหว่างการสังเคราะห์โมเดล CPLD (อุปกรณ์เป้าหมาย) จะได้รับการคัดเลือกและมีการสร้างรายการสุทธิในการทำแผนที่โดยใช้เทคโนโลยีรายการนี้สามารถปิดได้ - ปรับให้เข้ากับสถาปัตยกรรม CPLD ของแท้โดยใช้สถานที่และกระบวนการเส้นทางซึ่งโดยทั่วไปทำได้โดยซอฟต์แวร์สถานที่และเส้นทางของ บริษัท CPLD ซึ่งเป็นกรรมสิทธิ์ของ บริษัท จากนั้นผู้ปฏิบัติงานจะดำเนินกระบวนการยืนยันบางอย่างหากทุกอย่างดีเขาจะใช้ CPLD อย่างอื่น เขาจะจัดเรียงใหม่

ปัญหาด้านสถาปัตยกรรมของ CPLD

เมื่อพิจารณาถึงอุปกรณ์ลอจิกที่ตั้งโปรแกรมได้ซับซ้อนเพื่อใช้ในการออกแบบอาจมีปัญหาด้านสถาปัตยกรรมบางประการดังต่อไปนี้

- เทคโนโลยีการเขียนโปรแกรม

- ความสามารถในการบล็อกฟังก์ชัน

- ความสามารถ I / O

บางครอบครัวของ CPLD จากร้านค้าปลีกต่างๆ ได้แก่

- ตระกูล Altera MAX 7000 และ MAX 9000

- Atmel ATF และตระกูล ATV

- ตระกูล Lattice isp LSI

- Lattice (Vantis) ตระกูล MACH

- ตระกูล Xilinx XC9500

ครอบครัวของ CPLD

การประยุกต์ใช้ CPLD

แอปพลิเคชันของ CPLD มีดังต่อไปนี้

- อุปกรณ์ลอจิกที่ตั้งโปรแกรมได้ซับซ้อนเหมาะอย่างยิ่งสำหรับแอพพลิเคชั่นควบคุมที่มีประสิทธิภาพสูง

- CPLD สามารถใช้ในการออกแบบดิจิทัลเพื่อทำหน้าที่ของบูตโหลดเดอร์

- CPLD ใช้สำหรับโหลดข้อมูลการกำหนดค่าของเกตอาร์เรย์ที่ตั้งโปรแกรมได้จากหน่วยความจำแบบไม่ลบเลือน

- โดยทั่วไปจะใช้ในแอปพลิเคชันการออกแบบขนาดเล็กเช่นการถอดรหัสที่อยู่

- CPLD มักถูกใช้หลายแอปพลิเคชันเช่นในอุปกรณ์พกพาที่มีความไวต่อต้นทุนและใช้แบตเตอรี่เนื่องจากมีขนาดเล็กและใช้พลังงานต่ำ

ดังนั้นทั้งหมดนี้จึงเกี่ยวกับสถาปัตยกรรมอุปกรณ์ลอจิกที่ตั้งโปรแกรมได้และแอปพลิเคชันต่างๆ เราหวังว่าคุณจะเข้าใจแนวคิดนี้ดีขึ้น นอกจากนี้ข้อสงสัยใด ๆ เกี่ยวกับแนวคิดนี้หรือ เพื่อดำเนินโครงการไฟฟ้าและอิเล็กทรอนิกส์ โปรดให้ข้อเสนอแนะที่มีค่าของคุณโดยการแสดงความคิดเห็นในส่วนความคิดเห็นด้านล่าง คำถามสำหรับคุณว่า CPLD และ FPGA ต่างกันอย่างไร

เครดิตภาพ:

- CPLD วิกิมีเดีย

- สถาปัตยกรรมของ CPLD สไลด์ harecdn