RISC V เป็นสถาปัตยกรรมชุดคำสั่งที่พัฒนาโดยมหาวิทยาลัยแคลิฟอร์เนีย เบิร์กลีย์ แนวคิดของ RISC นั้นได้รับแรงบันดาลใจจากความจริงที่ว่าคำสั่งโปรเซสเซอร์ส่วนใหญ่ไม่ได้ถูกใช้โดยโปรแกรมคอมพิวเตอร์ส่วนใหญ่ ดังนั้น ตรรกะการถอดรหัสที่ไม่จำเป็นจึงถูกนำมาใช้ในการออกแบบของ โปรเซสเซอร์ ,กินไฟมากขึ้นตามพื้นที่. เพื่อย่นชุดคำสั่ง & เพื่อลงทุนเพิ่มเติมภายในทรัพยากรการลงทะเบียน โปรเซสเซอร์ RISC V ถูกนำไปใช้

เทคโนโลยีนี้สังเกตเห็นโดยยักษ์ใหญ่ด้านเทคโนโลยีและสตาร์ทอัพหลายรายเนื่องจากเป็นโอเพ่นซอร์สและฟรีทั้งหมด โปรเซสเซอร์ส่วนใหญ่มีข้อตกลงสิทธิ์การใช้งาน อย่างไรก็ตาม สำหรับโปรเซสเซอร์ประเภทนี้ ทุกคนสามารถออกแบบโปรเซสเซอร์ใหม่ได้ ดังนั้น บทความนี้จึงกล่าวถึงภาพรวมของโปรเซสเซอร์ RISC V – การทำงานและการใช้งาน

RISC V Processor คืออะไร?

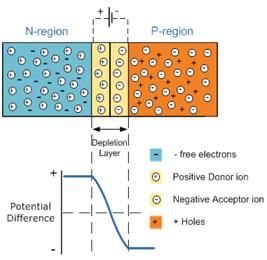

ในตัวประมวลผล RISC V คำว่า RISC ย่อมาจาก 'คอมพิวเตอร์ชุดคำสั่งที่ลดลง' ซึ่งรันคำสั่งคอมพิวเตอร์สองสามคำสั่งในขณะที่ 'V' หมายถึงรุ่นที่ 5 เป็นฮาร์ดแวร์โอเพ่นซอร์ส ISA (สถาปัตยกรรมชุดคำสั่ง) ตามหลักการที่กำหนดไว้ของ เสี่ยง .

เมื่อเทียบกับการออกแบบ ISA อื่นๆ ISA นี้มีให้พร้อมกับใบอนุญาตโอเพ่นซอร์ส ดังนั้น บริษัทผู้ผลิตหลายแห่งจึงได้ประกาศและจัดหาฮาร์ดแวร์ RISC-V ด้วยระบบปฏิบัติการโอเพ่นซอร์ส

นี่เป็นสถาปัตยกรรมใหม่และพร้อมใช้งานในใบอนุญาตแบบเปิด ไม่จำกัด และฟรี โปรเซสเซอร์นี้ได้รับการสนับสนุนอย่างกว้างขวางจากอุตสาหกรรมผู้ผลิตชิปและอุปกรณ์ ดังนั้นมันจึงได้รับการออกแบบเป็นหลักให้ขยายได้อย่างอิสระและปรับแต่งได้เพื่อใช้ในแอพพลิเคชั่นมากมาย

RISC V ประวัติ

RISC ถูกคิดค้นโดย Prof. David Patterson ประมาณปี 1980 ที่ University of California, Berkeley Prof. David และ Prof. John Hennessy ได้ส่งผลงานของพวกเขาในหนังสือสองเล่ม ได้แก่ “Computer Organization and Design” & “Computer Architecture at Stanford University ดังนั้นพวกเขาจึงได้รับ ACM A.M. รางวัลทัวริง ประจำปี 2560

ตั้งแต่ปี 2523 ถึงปี 2553 การวิจัยเพื่อการพัฒนารุ่นที่ห้าของ RISC ได้เริ่มต้นขึ้นและในที่สุดก็ถูกระบุเป็น RISC-V ซึ่งออกเสียงว่าเสี่ยงห้า

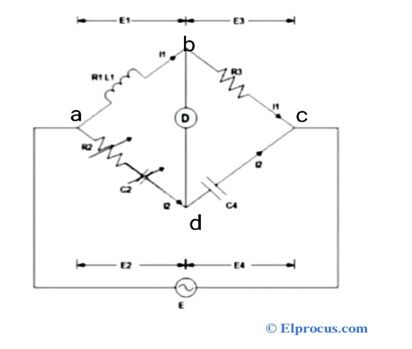

สถาปัตยกรรมและการทำงาน RISC V

สถาปัตยกรรม RV12 RISC V แสดงอยู่ด้านล่าง RV12 สามารถกำหนดค่าได้สูงด้วย CPU RISC แบบ single-core RV32I และ RV64I ซึ่งใช้ในฟิลด์ฝังตัว RV12 ยังมาจากตระกูล CPU 32 หรือ 64 บิต ขึ้นอยู่กับชุดคำสั่ง RISC-V มาตรฐานอุตสาหกรรม

RV12 ใช้งานสถาปัตยกรรมฮาร์วาร์ดเพื่อเข้าถึงคำสั่งและหน่วยความจำข้อมูลได้พร้อมกัน นอกจากนี้ยังมีไปป์ไลน์ 6 ขั้นตอนซึ่งช่วยในการเพิ่มประสิทธิภาพการทับซ้อนระหว่างการดำเนินการเช่นเดียวกับการเข้าถึงหน่วยความจำเพื่อปรับปรุงประสิทธิภาพ สถาปัตยกรรมนี้ส่วนใหญ่ประกอบด้วยการทำนายสาขา, แคชข้อมูล, หน่วยดีบัก, แคชคำสั่ง และหน่วยตัวคูณหรือตัวแบ่งที่เป็นตัวเลือก

คุณสมบัติหลักของ RV12 RISC V มีดังต่อไปนี้

- เป็นชุดคำสั่งมาตรฐานอุตสาหกรรม

- กำหนดพารามิเตอร์ด้วยข้อมูล 32 หรือ 64 บิต

- มีการขัดจังหวะที่แม่นยำและรวดเร็ว

- คำแนะนำที่กำหนดเองช่วยให้สามารถเพิ่มตัวเร่งฮาร์ดแวร์ที่เป็นกรรมสิทธิ์ได้

- การดำเนินการของรอบเดียว

- ไปป์ไลน์หกขั้นตอนพร้อมพับปรับให้เหมาะสม

- รองรับการป้องกันหน่วยความจำ

- แคชทางเลือกหรือแบบ Parameterized

- พารามิเตอร์อย่างยิ่ง

- ผู้ใช้สามารถเลือกข้อมูล 32/ 64 บิต & หน่วยคาดการณ์สาขา

- ผู้ใช้สามารถเลือกคำสั่ง/แคชข้อมูล

- โครงสร้างขนาดและสถาปัตยกรรมที่ผู้ใช้เลือกได้ของแคช

- Hardware Divider หรือ Multiplier Support โดยเวลาแฝงที่ผู้ใช้กำหนด

- สถาปัตยกรรมบัสมีความยืดหยุ่นซึ่งรองรับ Wishbone & AHB

- การออกแบบนี้ปรับกำลังและขนาดให้เหมาะสม

- การออกแบบได้รับการกำหนดพารามิเตอร์อย่างสมบูรณ์ซึ่งให้ประสิทธิภาพหรือการแลกเปลี่ยนพลังงาน

- การออกแบบ Gated CLK เพื่อลดพลังงาน

- รองรับซอฟต์แวร์ตามมาตรฐานอุตสาหกรรม

- เครื่องจำลองสถาปัตยกรรม

- Eclipse IDE ใช้สำหรับ Linux/ Windows

ท่อส่งการดำเนินการ RISC V

ประกอบด้วยห้าขั้นตอนเช่น IF (การดึงคำสั่ง) ID (ถอดรหัสคำสั่ง) EX (ดำเนินการ) MEM (การเข้าถึงหน่วยความจำ) และ WB (บันทึกการลงทะเบียน)

ดึงข้อมูลคำสั่ง

ในสเตจ Instruction Fetch หรือ IF คำสั่งเดียวจะถูกอ่านจากตัวนับโปรแกรม (PC) และหน่วยความจำคำสั่งซึ่งถูกอัพเดตเป็นคำสั่งถัดไป

คำแนะนำ ถอดรหัสล่วงหน้า

เมื่ออนุญาต RVC Support แล้ว ขั้นตอน Instruction Pre-Decode จะถอดรหัสคำสั่งที่บีบอัดแบบ 16 บิตเป็นคำสั่งแบบ 32 บิตแบบเนทีฟ

ถอดรหัสคำสั่ง

ในขั้นตอน Instruction Decode (ID) อนุญาตให้ Register File และควบคุม Bypass

ดำเนินการ

ในขั้นตอนการดำเนินการ ผลลัพธ์จะถูกคำนวณสำหรับคำสั่ง ALU, DIV, MUL หน่วยความจำที่อนุญาตสำหรับคำสั่ง Store หรือ Load และวัดสาขาและการกระโดดเทียบกับผลลัพธ์ที่คาดหวัง

หน่วยความจำ

ในสเตจหน่วยความจำนี้ หน่วยความจำถูกเข้าถึงผ่านไปป์ไลน์ การรวมเฟสนี้ทำให้มั่นใจได้ว่าไปป์ไลน์จะมีประสิทธิภาพสูง

เขียนกลับ

ในขั้นตอนนี้ ผลลัพธ์ของขั้นตอนการดำเนินการจะถูกเขียนลงในไฟล์ลงทะเบียน

เครื่องทำนายสาขา

โปรเซสเซอร์นี้ประกอบด้วยหน่วยทำนายสาขาหรือ BPU ที่ใช้ในการจัดเก็บข้อมูลที่ผ่านมาเพื่อเป็นแนวทางให้โปรเซสเซอร์ RISC V ตัดสินใจว่าจะใช้สาขาเฉพาะหรือไม่ ข้อมูลตัวทำนายนี้ได้รับการอัปเดตอย่างง่าย ๆ เมื่อสาขาดำเนินการ

หน่วยนี้ประกอบด้วยพารามิเตอร์ต่างๆ ที่กำหนดพฤติกรรมของมัน ตัวอย่างเช่น HAS_BPU ใช้เพื่อกำหนดว่าสาขาคาดการณ์ว่ามีหน่วยอยู่หรือไม่ BPU_GLOBAL_BITS จะกำหนดจำนวนบิตที่ผ่านมาที่จะใช้ และ BPU_LOCAL_BITS จะกำหนดจำนวน LSB ของตัวนับโปรแกรมที่ควรใช้ การรวมกันของ BPU_LOCAL_BITS & BPU_GLOBAL_BITS จะสร้างเวกเตอร์ที่ใช้เป็นหลักเพื่อจัดการกับ Branch-Prediction-Table

แคชข้อมูล

ส่วนใหญ่จะใช้เพื่อเพิ่มความเร็วในการเข้าถึงหน่วยความจำข้อมูลโดยการบัฟเฟอร์ตำแหน่งใหม่ของหน่วยความจำที่เข้าถึงได้ ความสามารถในการจัดการการเข้าถึงแบบครึ่งคำ ไบต์ และคำเมื่อ XLEN = 32 หากอยู่ในขอบเขตของตัวเอง นอกจากนี้ยังสามารถจัดการการเข้าถึงแบบ half-word, byte, word & double-word เมื่อ XLEN=64 หากอยู่ในขอบเขตของตัวเอง

ตลอดการพลาดแคช บล็อกทั้งหมดสามารถเขียนกลับไปยังหน่วยความจำได้ ดังนั้นหากจำเป็น บล็อกใหม่ก็สามารถโหลดลงในแคชได้ แคชข้อมูลถูกปิดใช้งานโดยการตั้งค่า DCACHE_SIZE เป็นศูนย์ หลังจากนั้นจะเข้าถึงตำแหน่งหน่วยความจำโดยตรงผ่าน อินเทอร์เฟซข้อมูล .

แคชคำสั่ง

ส่วนใหญ่จะใช้เพื่อเร่งการดึงคำสั่งโดยบัฟเฟอร์คำสั่งที่ดึงใหม่ แคชนี้ใช้เพื่อดึงพัสดุหนึ่งชิ้นสำหรับแต่ละรอบในขอบเขต 16 บิตใดๆ แต่ไม่ข้ามขอบเขตบล็อก ตลอดการแคชพลาด สามารถโหลดทั้งบล็อกจากหน่วยความจำคำสั่งได้ การกำหนดค่าของแคชนี้สามารถทำได้ตามความต้องการของผู้ใช้ ขนาดของแคช อัลกอริธึมการแทนที่ และความยาวของบล็อกสามารถกำหนดค่าได้

รอบคำสั่งจะถูกปิดการใช้งานโดยการตั้งค่า ICACHE_SIZE เป็นศูนย์ หลังจากนั้น พัสดุจะถูกดึงโดยตรงจากหน่วยความจำผ่าน อินเทอร์เฟซคำแนะนำ

หน่วยตรวจแก้จุดบกพร่อง

Debug Unit จะอนุญาตให้สภาพแวดล้อม Debug หยุดและตรวจสอบ CPU คุณสมบัติหลักของสิ่งนี้คือ Branch Tracing, Single Step Tracing มากถึง 8- Hardware Breakpoints

ลงทะเบียนไฟล์

ซึ่งได้รับการออกแบบโดยมีตำแหน่งลงทะเบียน 32 ตำแหน่งจาก X0 ถึง X31 โดยที่ X9 Register เป็นศูนย์เสมอ ไฟล์ Register ประกอบด้วย 1- เขียนพอร์ต & 2- อ่านพอร์ต

อินเทอร์เฟซที่กำหนดค่าได้

นี่คืออินเทอร์เฟซภายนอกที่โปรเซสเซอร์นี้สนับสนุนอินเทอร์เฟซบัสภายนอกที่แตกต่างกัน

RISC V ทำงานอย่างไร

RISC-V เป็นสถาปัตยกรรมชุดคำสั่งที่รูทภายในหลักการ RISC (คอมพิวเตอร์ชุดคำสั่งที่ลดลง) โปรเซสเซอร์นี้มีเอกลักษณ์เฉพาะตัวและยังปฏิวัติวงการอีกด้วย เนื่องจากเป็น ISA แบบโอเพ่นซอร์สที่ใช้งานได้ฟรี ทั่วไป ซึ่งฮาร์ดแวร์สามารถพัฒนาได้ ซอฟต์แวร์สามารถพอร์ต & โปรเซสเซอร์สามารถออกแบบให้รองรับได้

ความแตกต่าง B/W RISC V กับ MIPS

ความแตกต่างระหว่าง RISC V และ MIPS มีดังต่อไปนี้

|

RISC V |

MIPS |

| คำว่า RISC V ย่อมาจาก Reduced Instruction Set Computer โดยที่ 'V' เป็นรุ่นที่ห้า | คำว่า 'MIPS' หมายถึง 'ล้านคำสั่งต่อวินาที' |

| RISC-V อนุญาตให้ผู้ผลิตอุปกรณ์ขนาดเล็กออกแบบฮาร์ดแวร์โดยไม่ต้องจ่ายเงิน | MIPS อนุญาตให้ผู้ผลิตวัดความเร็วของโปรเซสเซอร์ด้วยการจ่ายเงินเพราะไม่ฟรี |

| MIPS ตายอย่างมีประสิทธิภาพ | RISC-V ไม่ตายอย่างมีประสิทธิภาพ |

| โปรเซสเซอร์นี้ให้คำแนะนำสาขาสำหรับการเปรียบเทียบสองรีจิสเตอร์ | MIPS ขึ้นอยู่กับคำสั่งเปรียบเทียบที่ตั้งค่ารีจิสเตอร์เป็น 1 หรือ 0 โดยขึ้นอยู่กับว่าคอนทราสต์เป็นจริงหรือไม่ |

| รูปแบบการเข้ารหัส ISA ได้รับการแก้ไข & ตัวแปรใน RISC V | รูปแบบการเข้ารหัส ISA ได้รับการแก้ไขใน MIPS |

| ขนาดชุดคำสั่งคือ 16 บิตหรือ 32 บิตหรือ 64 บิตหรือ 128 บิต | ขนาดชุดคำสั่งคือ 32 บิตหรือ 64 บิต |

| มี 32 วัตถุประสงค์ทั่วไป & การลงทะเบียนจุดลอยตัว | มี 31 วัตถุประสงค์ทั่วไปและการลงทะเบียนจุดลอยตัว |

| มีการดำเนินงานจุดลอยตัวที่มีความแม่นยำ 26 เดี่ยวและสองเท่า | มีการทำงานของจุดลอยตัวที่มีความแม่นยำ 15 เดียวและสองเท่า |

ความแตกต่าง B/W RISC V กับ ARM

ความแตกต่างระหว่าง RISC V Vs ARM มีดังต่อไปนี้

|

RISC V |

แขน |

| RISC-V เป็นโอเพ่นซอร์ส ดังนั้นจึงไม่จำเป็นต้องมีใบอนุญาตใดๆ | ARM เป็นโอเพ่นซอร์ส ดังนั้นจึงต้องมีใบอนุญาต |

| เป็นแพลตฟอร์มโปรเซสเซอร์ใหม่ ดังนั้นจึงมีการสนับสนุนซอฟต์แวร์และสภาพแวดล้อมการเขียนโปรแกรมน้อยมาก | ARM มีชุมชนออนไลน์ขนาดใหญ่มาก ซึ่งสนับสนุนไลบรารีและโครงสร้างเพื่อช่วยเหลือผู้ออกแบบเป้าหมายในแพลตฟอร์มต่างๆ เช่น ไมโครโปรเซสเซอร์ ไมโครคอนโทรลเลอร์ และเซิร์ฟเวอร์ |

| ชิปที่ใช้ RISC V-based ใช้พลังงาน 1 วัตต์ | ชิปที่ใช้ ARM ใช้พลังงานต่ำกว่า 4 วัตต์ |

| มีระบบการเข้ารหัส ISA แบบคงที่และแบบแปรผัน | มีระบบเข้ารหัส ISA คงที่ |

| ขนาดชุดคำสั่ง RISC V มีตั้งแต่ 16 บิตถึง 128 บิต | ขนาดคำสั่งมีตั้งแต่ 16 บิตถึง 64 บิต |

| ประกอบด้วย 32 วัตถุประสงค์ทั่วไปและการลงทะเบียนจุดลอยตัว | รวม 31 วัตถุประสงค์ทั่วไปและการลงทะเบียนจุดลอยตัว |

| มีการดำเนินงานจุดลอยตัวที่มีความแม่นยำ 26 จุด | มีการดำเนินการจุดลอยตัวที่มีความแม่นยำ 33 เดียว |

| มีการทำงานของจุดลอยตัวที่มีความแม่นยำ 26 เท่า | มีการทำงานของจุดลอยตัวที่มีความแม่นยำ 29 เท่า |

รหัส RISC V Verilog

รหัส verilog หน่วยความจำคำสั่งสำหรับ RISC แสดงอยู่ด้านล่าง

// รหัส Verilog สำหรับตัวประมวลผล RISC

// รหัส Verilog สำหรับหน่วยความจำคำสั่ง

โมดูล Instruction_Memory (

อินพุต[15:0] พีซี,

ผลลัพธ์[15:0] คำสั่ง

);

reg [`col – 1:0] หน่วยความจำ [`row_i – 1:0];

ลวด [3 : 0] rom_addr = พีซี[4 : 1];

อักษรย่อ

เริ่ม

$readmemb(“./test/test.prog”, หน่วยความจำ,0,14);

จบ

กำหนดคำสั่ง = หน่วยความจำ[rom_addr];

โมดูลปลาย

รหัส Verilog สำหรับโปรเซสเซอร์ RISC V 16 บิต:

โมดูล Risc_16_bit(

อินพุต clk

);

ลวดกระโดด, bne, beq, mem_read, mem_write, alu_src, reg_dst, mem_to_reg, reg_write;

ลวด[1:0] alu_op;

ลวด [3:0] opcode;

//ดาต้าพาธ

Datapath_Unit DU

(

.clk(clk),

.jump(กระโดด),

.frog(กบ),

.mem_read(mem_read),

.mem_write(mem_write),

.alu_src(alu_src),

.reg_dst(reg_dst),

.mem_to_reg(mem_to_reg),

.reg_write(reg_write),

.bne(bne),

.alu_op(alu_op),

.opcode(opcode)

);

// ชุดควบคุม

Control_Unit ควบคุม

(

.opcode(opcode),

.reg_dst(reg_dst),

.mem_to_reg(mem_to_reg),

.alu_op(alu_op),

.jump(กระโดด),

.bne(bne),

.frog(กบ),

.mem_read(mem_read),

.mem_write(mem_write),

.alu_src(alu_src),

.reg_write(reg_write)

);

โมดูลปลาย

ชุดคำสั่ง

ชุดคำสั่ง RISC V มีการกล่าวถึงด้านล่าง

การดำเนินการเลขคณิต

การดำเนินการเลขคณิต RISC V แสดงอยู่ด้านล่าง

| ช่วยในการจำ | พิมพ์ | คำแนะนำ | คำอธิบาย |

| เพิ่ม ถ, rs1, rs2 |

R |

เพิ่ม | rdß rs1 + rs2 |

| ย่อย rd, rs1, rs2 |

R |

ลบ | rdß rs1 – rs2 |

| ADDI rd, rs1, imm12 |

ฉัน |

เพิ่มทันที | rdß rs1 + imm12 |

| SLT ถ. rs1, rs2 |

R |

ตั้งค่าน้อยกว่า | rdß rs1 -< rs2 |

| SLTI ถ. rs1, imm12 |

ฉัน |

ตั้งน้อยกว่าทันที | rdß rs1 -< imm12 |

| SLTU ถ. rs1, rs2 |

R |

ตั้งน้อยกว่า unsigned | rdß rs1 -< rs2 |

| SLTIU rd, rs1, imm12 |

ฉัน |

ตั้งน้อยกว่าทันที unsigned | rdß rs1 -< imm12 |

| LUI rd, imm20 |

ใน |

โหลดบนทันที | rdß imm20<<12 |

| AUIP rd,imm20 |

ใน |

เพิ่มบนทันทีไปยัง PC | ที่ PC+imm20<<12 |

การดำเนินงานเชิงตรรกะ

การดำเนินการทางลอจิคัล RISC V มีการระบุไว้ด้านล่าง

| ช่วยในการจำ | พิมพ์ | คำแนะนำ | คำอธิบาย |

| และ rd, rs1, rs2 |

R |

และ | rdß rs1 & rs2 |

| หรือ rd, rs1, rs2 |

R |

หรือ | rdß rs1 | rs2 |

| XOR rd, rs1, rs2 |

R |

ฟรี | rdß rs1 ^ rs2 |

| ANDI rd, rs1, imm12 |

ฉัน |

และทันที | rdß rs1 & imm2 |

| ORI ถ. rs1, imm12 |

ฉัน |

หรือทันที | rdß rs1 | imm12 |

| OXRI ถ. rs1, imm12 |

ฉัน |

XOR ทันที | rdß rs1 ^ rs2 |

| SLL rd, rs1, rs2 |

R |

เลื่อนไปทางซ้ายตรรกะ | rdß rs1 << rs2 |

| SRL ถ, rs1, rs2 |

R |

เลื่อนไปทางขวาตรรกะ | rdß rs1 >> rs2 |

| RAS rd, rs1, rs2 |

R |

เลื่อนเลขคณิตไปทางขวา | rdß rs1 >> rs2 |

| SLLI rd, rs1, shamt |

ฉัน |

เลื่อนไปทางซ้ายตรรกะทันที | rdß rs1 << shamt |

| SRLI rd, rs1, shamt |

ฉัน |

เลื่อนไปทางขวาทันที | rdß rs1 >> shamt |

| ถนน SRAI, rs1, shamt |

ฉัน |

เลื่อนเลขคณิตไปทางขวาทันที | rdß rs1 >> shamt |

โหลด/จัดเก็บการดำเนินงาน

การดำเนินการโหลด/จัดเก็บ RISC V แสดงอยู่ด้านล่าง

| ช่วยในการจำ | พิมพ์ | คำแนะนำ | คำอธิบาย |

| LD ถ. imm12 (rs1) |

ฉัน |

โหลด doubleword | rdß mem [rs1 +imm12] |

| LW ถ. imm12 (rs1) |

ฉัน |

โหลดคำ | rdß mem [rs1 +imm12] |

| LH ถ. imm12 (rs1) |

ฉัน |

โหลดครึ่งทาง | rdß mem [rs1 +imm12] |

| LB rd, imm12 (rs1) |

ฉัน |

โหลดไบต์ | rdß mem [rs1 +imm12] |

| LWU ถ. imm12 (rs1) |

ฉัน |

โหลดคำ unsigned | rdß mem [rs1 +imm12] |

| ถ.LHU, imm12 (rs1) |

ฉัน |

โหลด unsigned ครึ่งคำ | rdß mem [rs1 +imm12] |

| LBU ถ. imm12 (rs1) |

ฉัน |

โหลดไบต์ที่ไม่ได้ลงนาม | rdß mem [rs1 +imm12] |

| SD rs2, imm12 (rs1) |

ส |

เก็บคำสองคำ | rs2 ถึง mem [rs1 +imm12] |

| SW rs2, imm12 (rs1) |

ส |

เก็บคำ | rs2 (31:0) ถึง mem [rs1 +imm12] |

| SH rs2, imm12 (rs1) |

ส |

เก็บครึ่งทาง | rs2 (15:0) ถึง mem [rs1 +imm12] |

| SB rs2, imm12 (rs1) |

ส |

จัดเก็บไบต์ | rs2 (15:0) ถึง mem [rs1 +imm12] |

| ถนน SRAI, rs1, shamt |

ฉัน |

เลื่อนเลขคณิตไปทางขวาทันที | rs2 (7:0) ถึง mem [rs1 +imm12] |

การดำเนินงานสาขา

การดำเนินการแยกสาขา RISC V แสดงไว้ด้านล่าง

| ช่วยในการจำ | พิมพ์ | คำแนะนำ | คำอธิบาย |

| BEQ rs1, rs2, imm12 |

SB |

สาขาเท่ากับ | ถ้า rs1== rs2 พีซี ß PC+imm12 |

| BNE rs1, rs2, imm12 |

SB |

สาขาไม่เท่ากัน | ถ้า rs1!= rs2 พีซี ß PC+imm12 |

| BGE rs1, rs2, imm12 |

SB |

สาขาที่มากกว่าหรือเท่ากับ | ถ้า rs1>= rs2 พีซี ß PC+imm12 |

| BGEU rs1, rs2, imm12 |

SB |

สาขาที่มากกว่าหรือเท่ากับ unsigned | ถ้า rs1>= rs2 พีซี ß PC+imm12 |

| BLT rs1, rs2, imm12 |

SB |

สาขาน้อยกว่า | ถ้า rs1< rs2 พีซี ß PC+imm12 |

| BLTU rs1, rs2, imm12 |

SB |

สาขาน้อยกว่า ไม่ได้ลงชื่อ | ถ้า rs1< rs2 พีซี ß PC+imm12 <<1 |

| JAL ถ, imm20 |

UJ |

กระโดดและลิงค์ | rdsPC+4 PCß PC+imm20 |

| JALR ถ, imm12(rs1) |

ฉัน |

กระโดดและเชื่อมโยงลงทะเบียน | rdsPC+4 PCß rs1+imm12 |

ข้อดี

ดิ ข้อดีของRISC ตัวประมวลผลวี รวมสิ่งต่อไปนี้

- ด้วยการใช้ RISCV เราสามารถประหยัดเวลาในการพัฒนา การพัฒนาซอฟต์แวร์ การตรวจสอบ ฯลฯ

- โปรเซสเซอร์นี้มีข้อดีหลายอย่าง เช่น ความเรียบง่าย ความเปิดกว้าง ความเป็นโมดูล การออกแบบที่สะอาดตา และความสามารถในการขยาย

- รองรับโดยคอมไพเลอร์หลายภาษาเช่น GCC (GNU Compiler Collection) คอมไพเลอร์ซอฟต์แวร์ฟรี & ผ่าน Linux OS .

- สามารถใช้โดยบริษัทต่างๆ ได้อย่างอิสระ เนื่องจากไม่มีค่าลิขสิทธิ์ ไม่มีค่าธรรมเนียมใบอนุญาต และไม่มีข้อผูกมัดใดๆ

- โปรเซสเซอร์ RISC-V ไม่ได้รวมคุณสมบัติใหม่หรือนวัตกรรมใดๆ เนื่องจากเป็นไปตามหลักการที่กำหนดไว้ของ RISC

- คล้ายกับ ISA อื่น ๆ ข้อมูลจำเพาะโปรเซสเซอร์นี้เพียงแค่กำหนดระดับชุดคำสั่งต่างๆ จึงมีตัวแปร 32 และ 64 บิต รวมถึงส่วนขยายเพื่อรองรับคำแนะนำจุดลอยตัว

- สิ่งเหล่านี้ฟรี เรียบง่าย แยกส่วน เสถียร ฯลฯ

ข้อเสีย

ดิ ข้อเสียของโปรเซสเซอร์ RISC V รวมสิ่งต่อไปนี้

- คำแนะนำที่ซับซ้อนมักใช้โดยคอมไพเลอร์และโปรแกรมเมอร์

- o/p ของ RISC อาจเปลี่ยนแปลงตามรหัสเมื่อคำสั่งที่ตามมาภายในลูปขึ้นอยู่กับคำสั่งก่อนหน้าสำหรับการดำเนินการ

- โปรเซสเซอร์เหล่านี้จำเป็นต้องบันทึกคำสั่งต่างๆ อย่างรวดเร็ว ซึ่งต้องใช้หน่วยความจำแคชขนาดใหญ่ที่ตั้งค่าเพื่อตอบสนองต่อคำสั่งภายในเวลาที่เหมาะสม

- คุณสมบัติ ความสามารถ และประโยชน์ของ RISC ทั้งหมดขึ้นอยู่กับสถาปัตยกรรมเป็นหลัก

แอปพลิเคชั่น

ดิ การประยุกต์ใช้ RISC V โปรเซสเซอร์ รวมสิ่งต่อไปนี้

- RISC-V ใช้ในระบบฝังตัว ปัญญาประดิษฐ์ และการเรียนรู้ของเครื่อง

- โปรเซสเซอร์เหล่านี้ใช้ในแอพพลิเคชั่นระบบฝังตัวที่มีประสิทธิภาพสูง

- โปรเซสเซอร์นี้เหมาะสมที่จะใช้ในบางสาขา เช่น Edge Computing, AI และแอพพลิเคชั่นสตอเรจ

- RISC-V มีความสำคัญเนื่องจากอนุญาตให้ผู้ผลิตอุปกรณ์รายเล็กออกแบบฮาร์ดแวร์โดยไม่ต้องจ่ายเงิน

- โปรเซสเซอร์นี้ช่วยให้นักวิจัยและนักพัฒนาสามารถออกแบบและวิจัยด้วยสถาปัตยกรรม ISA หรือชุดคำสั่งที่มีอยู่ได้ฟรี

- แอพพลิเคชั่นของ RISC V มีตั้งแต่ไมโครคอนโทรลเลอร์ฝังตัวขนาดเล็กไปจนถึงเดสก์ท็อปพีซีและซูเปอร์คอมพิวเตอร์ รวมถึงโปรเซสเซอร์เวคเตอร์

ดังนั้นนี่คือ ภาพรวมของโปรเซสเซอร์ RISC V – สถาปัตยกรรมการทำงานกับแอพพลิเคชั่น นี่คือคำถามสำหรับคุณ โปรเซสเซอร์ CISC คืออะไร?