ทรานซิสเตอร์ MOS เป็นองค์ประกอบพื้นฐานที่สุดในการออกแบบวงจรรวมขนาดใหญ่ โดยทั่วไปทรานซิสเตอร์เหล่านี้แบ่งออกเป็นสองประเภทคือ PMOS และ NMOS การรวมกันของทรานซิสเตอร์ NMOS และ PMOS เรียกว่า ทรานซิสเตอร์ CMOS . ความแตกต่าง ลอจิกเกต และอุปกรณ์ลอจิกดิจิทัลอื่น ๆ ที่นำมาใช้ต้องมีลอจิก PMOS เทคโนโลยีนี้มีราคาไม่แพงและมีความต้านทานต่อสัญญาณรบกวนได้ดี บทความนี้กล่าวถึงทรานซิสเตอร์ MOS ประเภทหนึ่ง เช่น ทรานซิสเตอร์ PMOS

PMOS ทรานซิสเตอร์คืออะไร?

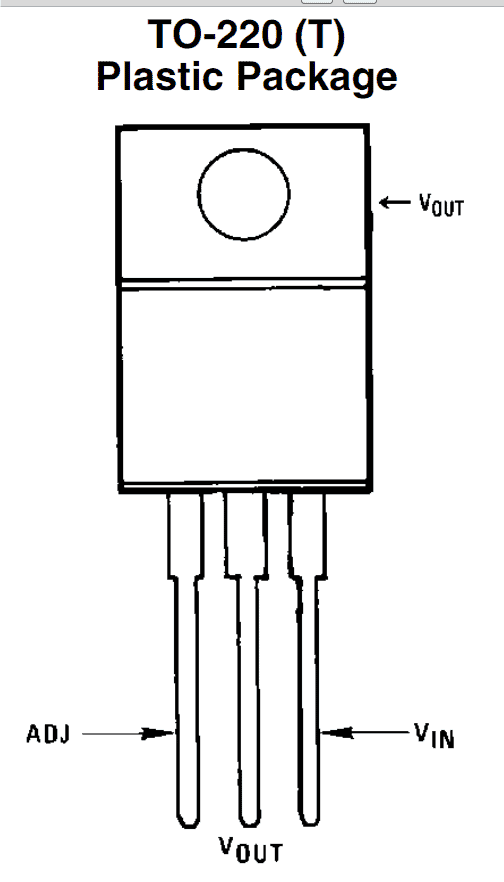

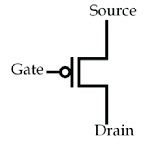

ทรานซิสเตอร์ PMOS หรือเซมิคอนดักเตอร์ออกไซด์ของโลหะ P-channel เป็นทรานซิสเตอร์ชนิดหนึ่งที่ใช้สารเจือปนชนิด p ในบริเวณช่องหรือเกต ทรานซิสเตอร์นี้เป็นสิ่งที่ตรงกันข้ามกับทรานซิสเตอร์ NMOS ทรานซิสเตอร์เหล่านี้มีสามขั้วหลัก แหล่งที่มา เกต & เดรนที่ซอร์สของทรานซิสเตอร์ได้รับการออกแบบด้วยซับสเตรตชนิด p และเทอร์มินอลเดรนได้รับการออกแบบด้วยซับสเตรตชนิด n ในทรานซิสเตอร์นี้ ตัวพาประจุเช่นรูมีหน้าที่รับผิดชอบในการนำกระแสไฟฟ้า สัญลักษณ์ทรานซิสเตอร์ PMOS แสดงไว้ด้านล่าง

PMOS ทรานซิสเตอร์ทำงานอย่างไร?

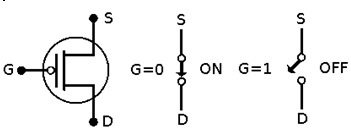

การทำงานของทรานซิสเตอร์ชนิด p นั้นค่อนข้างตรงกันข้ามกับทรานซิสเตอร์ชนิด n ทรานซิสเตอร์นี้จะสร้างวงจรเปิดเมื่อใดก็ตามที่ได้รับแรงดันไฟฟ้าที่ไม่มีค่าเล็กน้อย ซึ่งหมายความว่าไม่มีกระแสไฟฟ้าไหลจากขั้วเกท (G) ไปยังแหล่งกำเนิด (S) ในทำนองเดียวกัน ทรานซิสเตอร์นี้สร้างวงจรปิดเมื่อได้รับแรงดันไฟฟ้าประมาณ 0 โวลต์ ซึ่งหมายถึงกระแสไหลจากขั้วเกท (G) ไปยังเดรน (D)

ฟองสบู่นี้เรียกอีกอย่างว่าฟองผกผัน ดังนั้นหน้าที่หลักของวงกลมนี้คือการกลับค่าแรงดันไฟฟ้าอินพุต หากเทอร์มินอลเกตให้แรงดัน 1 อินเวอร์เตอร์นี้จะเปลี่ยนเป็นศูนย์และทำงานของวงจรตามนั้น ดังนั้นการทำงานของทรานซิสเตอร์ PMOS และทรานซิสเตอร์ NMOS จึงค่อนข้างตรงกันข้าม เมื่อเรารวมเข้าด้วยกันเป็นวงจร MOS เดียว มันจะกลายเป็นวงจร CMOS (complementary metal-oxide semiconductor)

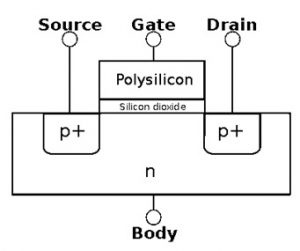

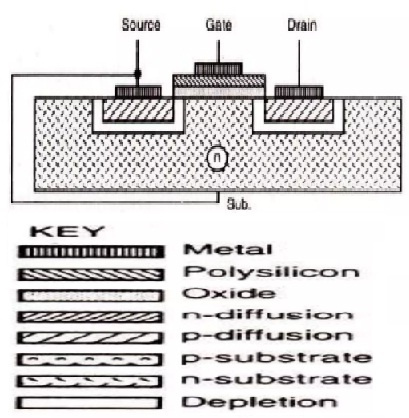

ภาพตัดขวางของทรานซิสเตอร์ PMOS

ภาพตัดขวางของทรานซิสเตอร์ PMOS แสดงไว้ด้านล่าง ทรานซิสเตอร์ pMOS ถูกสร้างขึ้นด้วยตัวแบบ n ซึ่งรวมถึงบริเวณเซมิคอนดักเตอร์แบบ p สองตัวซึ่งอยู่ติดกับเกท ทรานซิสเตอร์นี้มีเกตควบคุมตามที่แสดงในแผนภาพที่ควบคุมการไหลของอิเล็กตรอนระหว่างขั้วทั้งสอง เช่น แหล่งที่มาและท่อระบายน้ำ ในทรานซิสเตอร์ pMOS ตัวเครื่องจะอยู่ที่แรงดัน +ve เมื่อเทอร์มินอลเกตเป็นบวก เทอร์มินอลต้นทางและเดรนจะถูกไบอัสแบบย้อนกลับ เมื่อสิ่งนี้เกิดขึ้น จะไม่มีกระแสไหล ดังนั้นทรานซิสเตอร์จะปิด

เมื่อการจ่ายแรงดันไฟฟ้าที่เทอร์มินอลเกตลดระดับลงแล้ว ตัวพาที่มีประจุบวกจะถูกดึงดูดไปที่ด้านล่างของอินเทอร์เฟซ Si-SiO2 เมื่อใดก็ตามที่แรงดันไฟฟ้าต่ำเพียงพอ แชนเนลจะกลับด้านและสร้างเส้นทางนำไฟฟ้าจากเทอร์มินอลต้นทางไปยังเดรนโดยปล่อยให้กระแสไหล

เมื่อไรก็ตามที่ทรานซิสเตอร์เหล่านี้จัดการกับลอจิกดิจิทัล มักจะมีสองค่าที่แตกต่างกันเท่านั้น เช่น 1 & 0 (เปิดและปิด) แรงดันบวกของทรานซิสเตอร์เรียกว่า VDD ซึ่งแสดงถึงค่าลอจิกสูง (1) ภายในวงจรดิจิทัล ระดับแรงดัน VDD ใน ตรรกะ TTL โดยทั่วไปอยู่ที่ประมาณ 5V ในปัจจุบัน ทรานซิสเตอร์ไม่สามารถทนต่อแรงดันไฟฟ้าที่สูงเช่นนี้ได้ เนื่องจากโดยทั่วไปแล้วจะมีช่วงตั้งแต่ 1.5V – 3.3V แรงดันไฟฟ้าต่ำมักเรียกกันว่า GND หรือ VSS ดังนั้น VSS จึงหมายถึงลอจิก '0' และตั้งค่าตามปกติเป็น 0V

วงจรทรานซิสเตอร์ PMOS

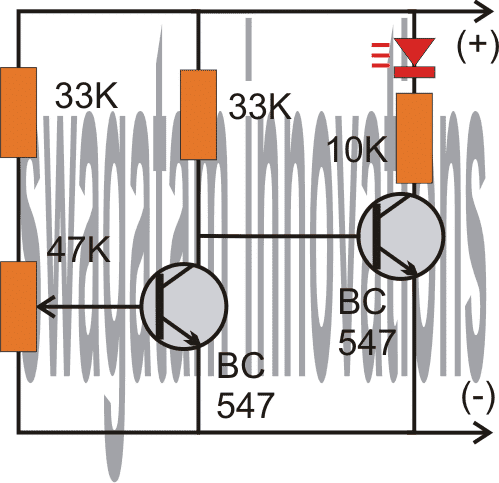

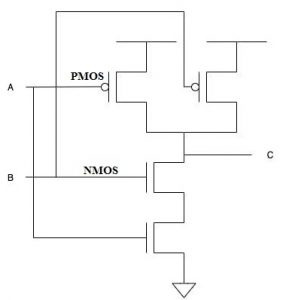

การออกแบบเกท NAND โดยใช้ทรานซิสเตอร์ PMOS และทรานซิสเตอร์ NMOS แสดงไว้ด้านล่าง โดยทั่วไปแล้ว NAND gate ในอุปกรณ์อิเล็กทรอนิกส์ดิจิทัลคือลอจิกเกต ซึ่งเรียกอีกอย่างว่า NOT-AND gate เอาต์พุตของเกทนี้มีค่าต่ำ (0) ก็ต่อเมื่ออินพุตสองตัวมีค่าสูง (1) และเอาต์พุตเป็นส่วนเสริมของเกท AND หากอินพุตใดในสองอินพุตมีค่าต่ำ (0) แสดงว่าจะให้ผลลัพธ์เอาต์พุตสูง

ในวงจรลอจิกด้านล่าง ถ้าอินพุต A เป็น 0 และ B เป็น 0 ดังนั้นอินพุตของ pMOS จะให้ค่า '1' และอินพุตของ nMOS จะให้ค่า '0' ดังนั้น ลอจิกเกตนี้จึงสร้างลอจิคัล '1' เนื่องจากเชื่อมต่อกับแหล่งที่มาด้วยวงจรปิดและแยกออกจาก GND ผ่านวงจรเปิด

เมื่อ A คือ '0' & B' คือ '1' ดังนั้น A input ของ pMOS จะสร้าง '1' และ A input ของ NMOS จะสร้าง '0' ดังนั้น เกทนี้จะสร้างลอจิคัลหนึ่งเพราะมันเชื่อมต่อกับแหล่งที่มาผ่านวงจรปิดและแยกออกจาก GND โดยวงจรเปิด เมื่อ A คือ '1' & B คือ '0' ดังนั้นอินพุต 'B' ของ pMOS จะสร้างเอาต์พุตสูง (1) & อินพุต 'B' ของ NMOS จะสร้างเอาต์พุตต่ำ (0) ดังนั้นลอจิกเกตนี้จะสร้างลอจิคัล 1 เนื่องจากเชื่อมต่อกับแหล่งที่มาผ่านวงจรปิดและแยกออกจาก GND โดยวงจรเปิด

เมื่อ A คือ '1' & B คือ '1' ดังนั้น A อินพุตของ' pMOS จะสร้างศูนย์ และอินพุตของ nMOS จะสร้าง '1' ดังนั้น เราควรตรวจสอบอินพุต B ของ pMOS & nMOS ด้วย อินพุต B ของ pMOS จะสร้าง '0' & อินพุต B ของ nMOS จะสร้าง '1' ดังนั้นลอจิกเกตนี้จะสร้างลอจิคัล '0' เนื่องจากแยกออกจากแหล่งที่มาโดยวงจรเปิดและเชื่อมต่อกับ GND ผ่านวงจรปิด

ตารางความจริง

ตารางความจริงของวงจรลอจิกด้านบนแสดงไว้ด้านล่าง

|

ก |

ข |

ค |

|

0 |

0 | 1 |

|

0 |

1 | 1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

แรงดันเกณฑ์ของทรานซิสเตอร์ PMOS โดยปกติจะเป็น 'Vgs' ซึ่งจำเป็นสำหรับการสร้างช่องสัญญาณที่เรียกว่าการผกผันช่องสัญญาณ ในทรานซิสเตอร์ PMOS ซับสเตรตและเทอร์มินอลต้นทางจะเชื่อมต่อกับ 'Vdd' อย่างง่ายดาย ถ้าเราเริ่มลดแรงดันไฟฟ้าโดยอ้างอิงกับเทอร์มินอลต้นทางที่เกตเทอร์มินอลจาก Vdd ไปยังจุดใดก็ตามที่คุณสังเกตเห็นการผกผันของช่องสัญญาณ ที่ตำแหน่งนี้หากคุณวิเคราะห์ว่า Vgs & ซอร์สอยู่ที่ศักย์ไฟฟ้าสูง คุณจะได้ค่าเป็นลบ ดังนั้นทรานซิสเตอร์ PMOS จึงมีค่า Vth เป็นลบ

กระบวนการผลิต PMOS

ขั้นตอนที่เกี่ยวข้องกับการประดิษฐ์ทรานซิสเตอร์ PMOS มีการกล่าวถึงด้านล่าง

ขั้นตอนที่ 1:

ชั้นเวเฟอร์ซิลิคอนบาง ๆ เปลี่ยนเป็นวัสดุประเภท N โดยการเติมวัสดุฟอสฟอรัส

ขั้นตอนที่ 2:

ชั้นซิลิกอนไดออกไซด์ (Sio2) หนาถูกปลูกบนซับสเตรตชนิด p ที่สมบูรณ์

ขั้นตอนที่ 3:

ตอนนี้พื้นผิวถูกเคลือบด้วยโฟโตเรสซิสต์บนชั้นซิลิกอนไดออกไซด์ที่หนา

ขั้นตอนที่ 4:

หลังจากนั้นชั้นนี้จะถูกแสง UV สัมผัสผ่านหน้ากากซึ่งกำหนดพื้นที่ที่การแพร่กระจายจะเกิดขึ้นพร้อมกับช่องทรานซิสเตอร์

ขั้นตอนที่ 5:

พื้นที่เหล่านี้จะถูกกัดออกไปพร้อมกับซิลิกอนไดออกไซด์ที่อยู่ข้างใต้ เพื่อให้พื้นผิวของแผ่นเวเฟอร์ถูกเปิดเผยภายในหน้าต่างที่กำหนดโดยมาสก์

ขั้นตอนที่ 6:

photoresist ที่เหลืออยู่จะถูกแยกออก & ชั้น Sio2 บาง ๆ จะเติบโตโดยทั่วไป 0.1 ไมโครเมตรทั่วพื้นผิวทั้งหมดของชิป หลังจากนั้นโพลีซิลิคอนจะถูกวางทับเพื่อสร้างโครงสร้างของประตู ช่างภาพจะวางบนชั้นโพลีซิลิคอนทั้งหมดและฉายแสง UV ผ่านหน้ากาก2

ขั้นตอนที่ 7:

การแพร่ทำได้โดยการให้ความร้อนเวเฟอร์จนถึงอุณหภูมิสูงสุดและผ่านก๊าซที่มีสิ่งสกปรกประเภท p ที่ต้องการ เช่น โบรอน

ขั้นตอนที่ 8:

ซิลิกอนไดออกไซด์ที่มีความหนา 1 ไมโครเมตรถูกปลูกขึ้นและมีการเคลือบวัสดุไวแสงไว้บนนั้น ฉายแสงอัลตราไวโอเลตด้วยหน้ากาก3 บนพื้นที่ที่ต้องการของประตู แหล่งที่มา และท่อระบายน้ำ ซึ่งสลักไว้เพื่อทำการตัดหน้าสัมผัส

ขั้นตอนที่ 9:

ตอนนี้โลหะหรืออลูมิเนียมถูกสะสมไว้บนพื้นผิวที่มีความหนา 1 ไมโครเมตร เป็นอีกครั้งที่มีการปลูกวัสดุโฟโตเรสซิสต์ไว้ทั่วโลหะและให้แสง UV ส่องผ่านหน้ากาก4 ซึ่งสลักไว้เพื่อสร้างการออกแบบการเชื่อมต่อโครงข่ายที่จำเป็น โครงสร้าง PMOS สุดท้ายแสดงไว้ด้านล่าง

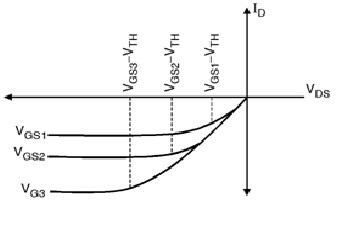

ลักษณะเฉพาะของทรานซิสเตอร์ PMOS

คุณลักษณะของทรานซิสเตอร์ PMOS IV-V แสดงไว้ด้านล่าง ลักษณะเหล่านี้ถูกแบ่งออกเป็นสองส่วนเพื่อให้ได้ความสัมพันธ์ระหว่างเดรนกับซอร์สกระแส (I DS) รวมถึงแรงดันของเทอร์มินัล เช่น ลิเนียร์ & โซนความอิ่มตัว

ในพื้นที่ซับ IDS จะเพิ่มขึ้นเชิงเส้นเมื่อ VDS (แรงดันเดรนไปยังแหล่งจ่าย) เพิ่มขึ้น ในขณะที่ในพื้นที่อิ่มตัว I DS จะเสถียรและไม่ขึ้นกับ VDS ความสัมพันธ์หลักระหว่าง ISD (แหล่งที่มาเพื่อระบายกระแส) และแรงดันไฟฟ้าของเทอร์มินัลนั้นได้มาจากขั้นตอนที่คล้ายกันของทรานซิสเตอร์ NMOS ในกรณีนี้ สิ่งเดียวที่จะเปลี่ยนแปลงคือตัวพาประจุที่อยู่ในชั้นผกผันเป็นเพียงรู เมื่อรูเคลื่อนจากแหล่งจ่ายไปยังท่อระบายน้ำ การไหลของกระแสก็เช่นกัน

ดังนั้น เครื่องหมายลบจึงปรากฏในสมการปัจจุบัน นอกจากนี้ ความโน้มเอียงที่ใช้ทั้งหมดที่ขั้วของอุปกรณ์จะเป็นค่าลบ ดังนั้น ID ของทรานซิสเตอร์ PMOS - คุณสมบัติ VDS แสดงไว้ด้านล่าง

สมการกระแสเดรนสำหรับทรานซิสเตอร์ PMOS ในพื้นที่เชิงเส้นจะได้รับเป็น:

ID = – mp ค็อกซ์

ในทำนองเดียวกัน สมการกระแสเดรนสำหรับทรานซิสเตอร์ PMOS ในบริเวณความอิ่มตัวจะได้รับเป็น:

ID = – mp Cox (VSG – | V TH |p )^2

โดยที่ 'mp' คือความคล่องตัวของหลุม & '|VTH| p’ คือแรงดันเกณฑ์ของทรานซิสเตอร์ PMOS

ในสมการข้างต้น เครื่องหมายลบจะระบุว่า ID( ระบายกระแส ) ไหลจากท่อระบายน้ำ (D) ไปยังแหล่งกำเนิด (S) ในขณะที่รูไหลไปในทิศทางตรงกันข้าม เมื่อการเคลื่อนที่ของรูต่ำเมื่อเทียบกับการเคลื่อนที่ของอิเล็กตรอน ทรานซิสเตอร์ PMOS จะได้รับผลกระทบจากความสามารถของตัวขับกระแสต่ำ

ดังนั้น ทั้งหมดนี้เป็นเรื่องเกี่ยวกับภาพรวมของทรานซิสเตอร์ PMOS หรือ p-type mos transistor – โครงสร้าง วงจร และการทำงานของมัน PMOS ทรานซิสเตอร์ได้รับการออกแบบ ด้วย p-source, n-substrate และเดรน ผู้ให้บริการชาร์จของ PMOS เป็นรู ทรานซิสเตอร์นี้นำไฟฟ้าเมื่อจ่ายแรงดันต่ำที่เทอร์มินอลเกท อุปกรณ์ที่ใช้ PMOS มีแนวโน้มที่จะถูกรบกวนน้อยกว่าเมื่อเทียบกับอุปกรณ์ NMOS ทรานซิสเตอร์เหล่านี้สามารถใช้เป็นตัวต้านทานที่ควบคุมแรงดันไฟฟ้า โหลดที่ใช้งานอยู่ มิเรอร์ปัจจุบัน เครื่องขยายสัญญาณทรานส์อิมพีแดนซ์ และยังใช้ในสวิตช์และเครื่องขยายแรงดันไฟฟ้าอีกด้วย นี่คือคำถามสำหรับคุณ ทรานซิสเตอร์ NMOS คืออะไร