ตัวสร้างความเท่าเทียมกันและฟังก์ชันหลักของตัวตรวจสอบความเท่าเทียมกันคือการตรวจจับข้อผิดพลาดในการส่งข้อมูลและแนวคิดนี้ถูกนำมาใช้ในปี 1922 ในเทคโนโลยี RAID จะใช้บิตพาริตีและตัวตรวจสอบความเท่าเทียมกันเพื่อป้องกันข้อมูลสูญหาย พาริตีบิตเป็นบิตพิเศษที่กำหนดไว้ที่ด้านการส่งข้อมูลเป็น '0' หรือ '1' ซึ่งใช้เพื่อตรวจจับข้อผิดพลาดบิตเดียวเท่านั้นและเป็นวิธีที่ง่ายที่สุดในการตรวจจับข้อผิดพลาด มีรหัสตรวจจับข้อผิดพลาดประเภทต่างๆที่ใช้ในการตรวจจับข้อผิดพลาด ได้แก่ พาริตี, ตัวนับวงแหวน, รหัสพาริตีบล็อก, รหัสแฮมมิง, ไบนารีเป็นต้นคำอธิบายสั้น ๆ เกี่ยวกับพาริตีบิตพาริตี เครื่องกำเนิดไฟฟ้า และตัวตรวจสอบมีคำอธิบายด้านล่าง

Parity Bit คืออะไร?

คำจำกัดความ: บิตพาริตีหรือบิตตรวจสอบคือบิตที่เพิ่มเข้าไปในรหัสไบนารีเพื่อตรวจสอบว่ารหัสเฉพาะนั้นอยู่ในพาริตีหรือไม่เช่นรหัสนั้นอยู่ในพาริตีแบบคู่หรือพาริตีคี่ถูกตรวจสอบโดยบิตตรวจสอบหรือบิตพาริตีนี้ ความเท่าเทียมกันคืออะไรนอกจากจำนวน 1 และมีพาริตีบิตสองประเภทคือบิตและบิตคี่

ในบิตพาริตีคี่รหัสจะต้องเป็นเลขคี่ของ 1 ตัวอย่างเช่นเรากำลังใช้รหัส 5 บิต 100011 รหัสนี้ถูกกล่าวว่าเป็นเลขคู่เพราะมีเลข 1 สามตัวในรหัสที่เรานำมา . ในบิตพาริตีรหัสจะต้องเป็นเลขคู่ของ 1 ตัวอย่างเช่นเรากำลังใช้รหัส 6 บิต 101101 รหัสนี้มีความเท่าเทียมกันเนื่องจากมีเลข 1 อยู่สี่ตัวในรหัสที่เรานำมา

Parity Generator คืออะไร?

คำจำกัดความ: พาริตีเจเนอเรเตอร์เป็นวงจรรวมที่เครื่องส่งโดยใช้ข้อความต้นฉบับเป็นอินพุตและสร้างพาริตีบิตสำหรับข้อความนั้นและตัวส่งในตัวสร้างนี้จะส่งข้อความพร้อมกับพาริตีบิต

ประเภทของ Parity Generator

การจำแนกประเภทของเครื่องกำเนิดไฟฟ้านี้แสดงไว้ในรูปด้านล่าง

ประเภทของความเท่าเทียมกันของเครื่องกำเนิดไฟฟ้า

แม้แต่ Parity Generator

ตัวสร้างความเท่าเทียมกันจะเก็บรักษาข้อมูลไบนารีไว้ในเลขคู่ของ 1 ตัวอย่างเช่นข้อมูลที่ถ่ายเป็นเลขคี่ของ 1 ตัวสร้างพาริตีแบบคู่นี้จะรักษาข้อมูลเป็นเลขคู่ของ 1 โดยการเพิ่ม 1 พิเศษให้กับคี่ จำนวน 1 ตัว นอกจากนี้ยังเป็นวงจรรวมที่มีเอาต์พุตขึ้นอยู่กับข้อมูลอินพุตที่กำหนดซึ่งหมายความว่าข้อมูลอินพุตเป็นข้อมูลไบนารีหรือรหัสไบนารีที่กำหนดสำหรับตัวสร้างพาริตี

ให้เราพิจารณาข้อมูลไบนารีอินพุตสามตัวซึ่งสามบิตถือเป็น A, B และ C เราสามารถเขียนได้ 23ชุดค่าผสมโดยใช้ข้อมูลไบนารีอินพุตสามชุดที่มีค่าตั้งแต่ 000 ถึง 111 (0 ถึง 7) ชุดค่าผสมทั้งหมดแปดชุดจะได้รับจากข้อมูลไบนารีอินพุตสามชุดที่เราได้พิจารณา ตารางความจริงของตัวสร้างพาริตีสำหรับข้อมูลไบนารีอินพุตสามตัวแสดงอยู่ด้านล่าง

0 0 0 - ในรหัสไบนารีอินพุตนี้ความเท่าเทียมกันจะถูกนำมาใช้เป็น '0' เนื่องจากอินพุตอยู่ในความเท่าเทียมกันแล้วดังนั้นจึงไม่จำเป็นต้องเพิ่มความเท่าเทียมกันอีกครั้งสำหรับอินพุตนี้

0 0 1 - - ในรหัสไบนารีที่ป้อนนี้มีเพียงตัวเลข ‘1’ ตัวเดียวและตัวเลขเดียวของ ‘1’ คือจำนวนคี่ของ ‘1’ หากมีจำนวนคี่ของ '1' อยู่ที่นั่นแม้แต่ตัวสร้างพาริตีจะต้องสร้าง '1' อีกตัวหนึ่งเพื่อทำให้เป็นเลขคู่ดังนั้นความเท่าเทียมกันจะถูกนำมาเป็น 1 เพื่อทำให้รหัส 0 0 1 เป็นความเท่าเทียมกัน

0 1 0 - บิตนี้อยู่ในความเท่าเทียมกันแบบคี่ดังนั้นความเท่าเทียมกันจึงถูกนำมาเป็น 1 เพื่อทำให้รหัส 0 1 0 เป็นความเท่าเทียมกัน

0 1 1 - บิตนี้อยู่ในความเท่าเทียมกันแล้วดังนั้นความเท่าเทียมกันจะถูกนำมาเป็น 0 เพื่อทำให้รหัส 0 1 1 เป็นความเท่าเทียมกัน

1 0 0 - บิตนี้อยู่ในความเท่าเทียมกันแบบคี่ดังนั้นความเท่าเทียมกันจะถูกนำมาเป็น 1 เพื่อทำให้รหัส 1 0 0 เป็นความเท่าเทียมกัน

1 0 1 - บิตนี้อยู่ในความเท่าเทียมกันแล้วดังนั้นแม้พาริตีจะถูกนำมาเป็น 0 เพื่อทำให้โค้ด 1 0 1 เป็นพาริตีแบบคู่

1 1 0 - บิตนี้ยังอยู่ในความเท่าเทียมกันดังนั้นแม้พาริตีจะถูกนำมาเป็น 0 เพื่อทำให้โค้ด 1 1 0 เป็นพาริตี

1 1 1 - บิตนี้อยู่ในความเสมอภาคแบบคี่ดังนั้นความเท่าเทียมกันจะถูกนำมาเป็น 1 เพื่อทำให้รหัส 1 1 1 เป็นความเท่าเทียมกัน

แม้แต่ตารางความจริงของ Parity Generator

| กขค | แม้แต่ Parity |

| 0 0 0 | 0 |

| 0 0 1 | 1 |

| 0 1 0 | 1 |

| 0 1 1 | 0 |

| 1 0 0 | 1 |

| 1 0 1 | 0 |

| 1 1 0 | 0 |

| 1 1 1 | 1 |

แผนที่ karnaugh (k-map) การทำให้เข้าใจง่ายสำหรับการป้อนข้อมูลสามบิตแม้ความเท่าเทียมกันคือ

k-map-for-even-parity-generator

จากตารางความจริงความเท่าเทียมกันด้านบนนิพจน์พาริตีบิตแบบง่ายถูกเขียนเป็น

นิพจน์ความเท่าเทียมกันที่ดำเนินการโดยใช้ประตู Ex-OR สองประตูและแผนภาพตรรกะของความเท่าเทียมกันนี้โดยใช้ Ex-OR ประตูลอจิก ดังแสดงด้านล่าง

แม้กระทั่งพาริตี - ลอจิก - วงจร

ด้วยวิธีนี้ตัวสร้างความเท่าเทียมกันจะสร้างเลขคู่ของ 1 โดยการรับข้อมูลอินพุต

Odd Parity Generator

ตัวสร้างพาริตีคี่จะเก็บรักษาข้อมูลไบนารีไว้ในจำนวนคี่ของ 1 ตัวอย่างเช่นข้อมูลที่ถ่ายเป็นเลขคู่ของ 1 ตัวสร้างพาริตีคี่นี้จะรักษาข้อมูลเป็นจำนวนคี่ของ 1 โดยการเพิ่ม 1 พิเศษเข้าไป เลขคู่ของ 1 นี่คือวงจรรวมที่มีเอาต์พุตขึ้นอยู่กับข้อมูลอินพุตที่กำหนดเสมอ หากมีเลขคู่ของ 1 จะมีการเพิ่มเพียงบิตพาริตีเพื่อทำให้รหัสไบนารีเป็นเลขคี่ของ 1

ให้เราพิจารณาข้อมูลไบนารีอินพุตสามตัวซึ่งสามบิตถือเป็น A, B และ C ตารางความจริงของตัวสร้างพาริตีคี่สำหรับข้อมูลไบนารีอินพุตสามรายการแสดงอยู่ด้านล่าง

0 0 0 - ในรหัสไบนารีอินพุตนี้พาริตีคี่จะถูกนำมาใช้เป็น '1' เนื่องจากอินพุตอยู่ในรูปแบบความเท่าเทียมกัน

0 0 1 - อินพุตไบนารีนี้อยู่ในความเสมอภาคแบบคี่ดังนั้นจึงถือว่าความเท่าเทียมกันเป็น 0

0 1 0 - อินพุตไบนารีนี้อยู่ในความเสมอภาคแบบคี่เช่นกันดังนั้นจึงถือว่าความเท่าเทียมกันเป็น 0

0 1 1 - บิตนี้อยู่ในความเท่าเทียมกันดังนั้นความเท่าเทียมกันจะถูกนำมาเป็น 1 เพื่อทำให้รหัส 0 1 1 เป็นพาริตีแบบคี่

1 0 0 - บิตนี้อยู่ในความเสมอภาคแบบคี่แล้วดังนั้นความเท่าเทียมกันจะถูกนำมาเป็น 0 เพื่อทำให้รหัส 1 0 0 เป็นพาริตีแบบคี่

1 0 1 - บิตอินพุตนี้อยู่ในความเท่าเทียมกันดังนั้นความเท่าเทียมกันจะถูกนำมาเป็น 1 เพื่อทำให้รหัส 1 0 1 เป็นพาริตีแบบคี่

1 1 0 - บิตนี้อยู่ในความเท่าเทียมกันดังนั้นพาริตีคี่จึงถูกนำมาเป็น 1

1 1 1 - บิตอินพุตนี้อยู่ในรูปแบบคี่พาริตีจึงถูกนำมาเป็น o

ตารางความจริงของ Odd Parity Generator

| กขค | ความเท่าเทียมกันที่แปลกประหลาด |

| 0 0 0 | 1 |

| 0 0 1 | 0 |

| 0 1 0 | 0 |

| 0 1 1 | 1 |

| 1 0 0 | 0 |

| 1 0 1 | 1 |

| 1 1 0 | 1 |

| 1 1 1 | 0 |

การทำให้เข้าใจง่ายของแผนที่ Kavanaugh (k-map) สำหรับการป้อนข้อมูลแบบคี่สามบิตคือ

k-map-for-odd-parity-generator

จากตารางความจริงพาริตีแปลก ๆ ข้างต้นนิพจน์พาริตีบิตแบบง่ายถูกเขียนเป็น

แผนภาพตรรกะของตัวสร้างพาริตีแปลก ๆ นี้แสดงไว้ด้านล่าง

วงจรลอจิก

ด้วยวิธีนี้ตัวสร้างพาริตีคี่จะสร้างเลขคี่ของ 1 โดยรับข้อมูลอินพุต

Parity Check คืออะไร?

คำจำกัดความ: วงจรผสมที่เครื่องรับคือตัวตรวจสอบความเท่าเทียมกัน ตัวตรวจสอบนี้รับข้อความที่ได้รับรวมทั้งพาริตีบิตเป็นอินพุต จะให้เอาต์พุตเป็น '1' หากพบข้อผิดพลาดและให้เอาต์พุตเป็น '0' หากไม่พบข้อผิดพลาดในข้อความรวมถึงพาริตีบิต

ประเภทของ Parity Checker

การจำแนกประเภทของตัวตรวจสอบความเท่าเทียมกันจะแสดงในรูปด้านล่าง

types-of-parity-checker

แม้แต่ Parity Checker

ในตัวตรวจสอบความเท่าเทียมกันหากบิตข้อผิดพลาด (E) เท่ากับ ‘1’ แสดงว่าเรามีข้อผิดพลาด หากบิตข้อผิดพลาด E = 0 แสดงว่าไม่มีข้อผิดพลาด

Error Bit (E) = 1 เกิดข้อผิดพลาด

Error Bit (E) = 0 ไม่มีข้อผิดพลาด

วงจรตรวจสอบความเท่าเทียมกันแสดงในรูปด้านล่าง

วงจรลอจิก

Odd Parity Checker

ในตัวตรวจสอบความเท่าเทียมกันแบบคี่หากบิตข้อผิดพลาด (E) เท่ากับ ‘1’ แสดงว่าไม่มีข้อผิดพลาด หากบิตข้อผิดพลาด E = 0 แสดงว่ามีข้อผิดพลาด

Error Bit (E) = 1 ไม่มีข้อผิดพลาด

Error Bit (E) = 0 เกิดข้อผิดพลาด

ตัวตรวจสอบความเท่าเทียมกันจะไม่สามารถตรวจจับได้หากมีข้อผิดพลาดมากกว่า '1' บิตและไม่สามารถแก้ไขข้อมูลได้อย่างถูกต้องสิ่งเหล่านี้เป็นข้อเสียเปรียบหลักของตัวตรวจสอบความเท่าเทียมกัน

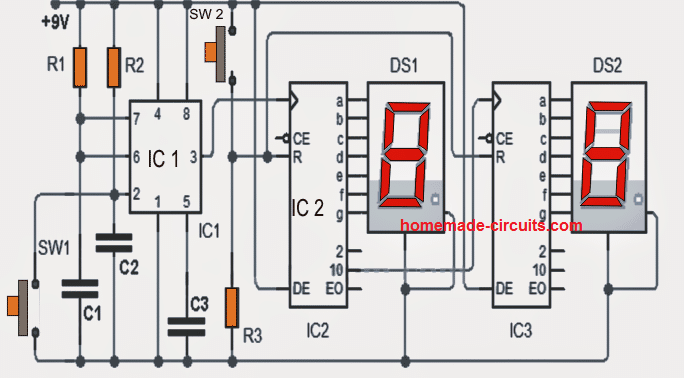

Parity Generator / Checker โดยใช้ IC’s

IC 74180 ทำหน้าที่ของการสร้างพาริตีเช่นเดียวกับการตรวจสอบ 9 บิต (8 บิตข้อมูล, 1 พาริตีบิต) Parity Generator / Checker แสดงอยู่ในรูปด้านล่าง

IC-74180

IC 74180 ประกอบด้วยบิตข้อมูลแปดบิต (X0ถึง X7), Vกระแสตรง,อินพุตคู่, อินพุตคี่, เอาต์พุตเซเว่น, เอาต์พุตคี่ S และพินกราวด์

หากอินพุตคู่และคี่ที่กำหนดมีค่าสูง (H) ดังนั้นเอาต์พุตคู่และคี่ทั้งคู่จะต่ำ (L) ในทำนองเดียวกันหากอินพุตที่ระบุทั้งคู่เป็นต่ำ (L) ดังนั้นเอาต์พุตคู่และคี่จะสูง ( H).

ข้อดีของ Parity

ข้อดีของความเท่าเทียมกันคือ

- ความเรียบง่าย

- ง่ายต่อการใช้

การใช้งาน ของ Parity

การประยุกต์ใช้ความเท่าเทียมกันคือ

- ใน ระบบดิจิทัล และแอปพลิเคชันฮาร์ดแวร์จำนวนมากจะใช้ความเท่าเทียมกันนี้

- พาริตีบิตยังใช้ใน Small Computer System Interface (SCSI) และใน Peripheral Component Interconnect (PCI) เพื่อตรวจจับข้อผิดพลาด

คำถามที่พบบ่อย

1). อะไรคือความแตกต่างระหว่างตัวสร้างความเท่าเทียมกันและตัวตรวจสอบความเท่าเทียมกัน?

ตัวสร้างพาริตีจะสร้างพาริตีบิตในเครื่องส่งและตัวตรวจสอบความเท่าเทียมกันจะตรวจสอบบิตพาริตีในเครื่องรับ

2). ไม่มีความเท่าเทียมกันหมายความว่าอย่างไร

เมื่อไม่ได้ใช้พาริตีบิตเพื่อตรวจสอบข้อผิดพลาดแล้วพาริตีบิตจะถูกกล่าวว่าเป็น non-parity หรือไม่มีพาริตีหรือไม่มีพาริตี

3). ค่าพาริตีคืออะไร?

แนวคิดมูลค่าความเท่าเทียมกันที่ใช้สำหรับสินค้าและหลักทรัพย์และคำนี้หมายถึงเมื่อมูลค่าของสินทรัพย์ทั้งสองเท่ากัน

4). ทำไมเราต้องมีตัวตรวจสอบความเท่าเทียมกัน?

จำเป็นต้องใช้ตัวตรวจสอบความเท่าเทียมกันเพื่อตรวจจับข้อผิดพลาดในการสื่อสารและในตัวตรวจสอบความเท่าเทียมกันของอุปกรณ์จัดเก็บข้อมูลหน่วยความจำก็ใช้สำหรับการทดสอบ

5). พาริตีบิตตรวจจับหน่วยข้อมูลที่เสียหายได้อย่างไร

บิตที่ซ้ำซ้อนในเทคนิคนี้เรียกว่าพาริตีบิตตรวจจับหน่วยข้อมูลที่เสียหายเมื่อเกิดข้อผิดพลาดระหว่างการส่งข้อมูล

ในบทความนี้วิธีการ ความเท่าเทียมกัน เครื่องกำเนิดและตัวตรวจสอบสร้างและตรวจสอบบิตและประเภทของมันวงจรลอจิกตารางความจริงและนิพจน์ k-map จะกล่าวถึงสั้น ๆ นี่คือคำถามสำหรับคุณคุณจะคำนวณความเท่าเทียมกันและคี่ได้อย่างไร?