ในโพสต์นี้ เราจะมาเรียนรู้วิธีสร้างเกทลอจิก NOT, AND, NAND, OR และ NOR โดยใช้ทรานซิสเตอร์แบบแยกส่วน ข้อได้เปรียบหลักของการใช้ลอจิกเกตของทรานซิสเตอร์คือสามารถทำงานได้แม้ในแรงดันไฟฟ้าที่ต่ำถึง 1.5 V

ในการใช้งานอิเล็กทรอนิกส์บางอย่าง แรงดันไฟฟ้าที่ใช้ได้อาจไม่เพียงพอต่อการจ่ายไฟให้กับ TTL หรือแม้แต่ไอซี CMOS โดยเฉพาะอย่างยิ่งสำหรับอุปกรณ์ที่ใช้แบตเตอรี่ ไม่ต้องสงสัยเลย คุณมีตัวเลือก IC ลอจิก 3 โวลต์เสมอ อย่างไรก็ตาม สิ่งเหล่านี้ไม่สามารถเข้าถึงได้ง่ายสำหรับผู้ที่ชื่นชอบหรือผู้ทดลอง และพวกเขาไม่ได้ทำงานภายใต้ข้อกำหนดแรงดันไฟฟ้าที่กำหนดไว้ (โดยทั่วไปจะต่ำกว่า 2.5 โวลต์ DC)

นอกจากนี้ อาจมีที่สำหรับแบตเตอรี่ 1.5 โวลต์เพียงก้อนเดียวในแอปพลิเคชันที่ใช้พลังงานจากแบตเตอรี่ อืม แล้วจะทำไงดี? โดยปกติ IC ลอจิกเกต อาจถูกแทนที่ด้วยลอจิกเกตแบบทรานซิสเตอร์ สำหรับลอจิกเกตแต่ละอัน โดยทั่วไปจำเป็นต้องมีทรานซิสเตอร์เพียงสองสามตัว และสำหรับลอจิกอินเวอร์เตอร์เกททั่วไป จำเป็นต้องมีทรานซิสเตอร์เพียงตัวเดียว

FETs กับทรานซิสเตอร์แบบไบโพลาร์

ทรานซิสเตอร์สนามผล (FETs) vs ทรานซิสเตอร์สองขั้ว : ตัวเลือกใดดีกว่าสำหรับวงจรลอจิกแรงดันต่ำ คุณสมบัติที่ยอดเยี่ยมอย่างหนึ่งของ ข้อเท็จจริง คือความต้านทาน 'เปิด' ของพวกเขาต่ำอย่างไม่น่าเชื่อ นอกจากนี้พวกเขาต้องการกระแสไฟเปิดที่ต่ำมาก

อย่างไรก็ตาม มีข้อ จำกัด ประการหนึ่งในการใช้งานที่มีแรงดันไฟฟ้าต่ำมาก โดยทั่วไป ขีดจำกัดแรงดันเกตคือหนึ่งโวลต์หรือมากกว่านั้น นอกจากนี้ แรงดันไฟฟ้าที่ใช้ได้อาจลดลงต่ำกว่าช่วงการทำงานที่เหมาะสมที่สุดของ FET หากติดตั้งตัวต้านทานแบบจำกัดกระแสหรือแบบดึงลงเข้ากับเกต

ในทางกลับกัน ทรานซิสเตอร์แบบสวิตชิ่งแบบไบโพลาร์มีข้อได้เปรียบในการใช้งานแบตเตอรี่เดี่ยวที่มีแรงดันไฟฟ้าต่ำมาก เนื่องจากต้องใช้ไฟเพียง 0.6 ถึง 0.7 โวลต์ในการเปิดเครื่อง

นอกจากนี้ FET ทั่วไปส่วนใหญ่ซึ่งปกติจะขายเป็น Bubble Pack ที่ร้านขายอุปกรณ์อิเล็กทรอนิกส์ใกล้บ้านคุณมักจะมีราคาสูงกว่าทรานซิสเตอร์แบบไบโพลาร์ นอกจากนี้ยังสามารถซื้อแพ็คเก็ตทรานซิสเตอร์แบบไบโพลาร์จำนวนมากได้ในราคา FET หนึ่งคู่

การจัดการ FET จำเป็นต้องมีการดูแลมากกว่าการจัดการทรานซิสเตอร์แบบไบโพลาร์อย่างมีนัยสำคัญ ไฟฟ้าสถิตและการใช้ในทางที่ผิดในการทดลองทั่วไปทำให้ FET มีแนวโน้มที่จะเกิดความเสียหายได้ง่าย ส่วนประกอบที่ถูกไฟไหม้อาจทำลายช่วงเวลาเย็นที่สนุกสนานและสร้างสรรค์ของการทดลองหรือนวัตกรรม เพื่อไม่ให้ลืมความเจ็บปวดทางอารมณ์ของการดีบัก

พื้นฐานของการสลับทรานซิสเตอร์

ตัวอย่างวงจรลอจิกที่อธิบายในบทความนี้ใช้ประโยชน์จากทรานซิสเตอร์สองขั้ว NPN เนื่องจากมีราคาไม่แพงและไม่ต้องการการจัดการพิเศษ เพื่อหลีกเลี่ยงความเสียหายต่ออุปกรณ์หรือชิ้นส่วนที่รองรับ ควรใช้มาตรการด้านความปลอดภัยที่เหมาะสมก่อนเชื่อมต่อวงจรของคุณ

แม้ว่าวงจรของเราจะมีศูนย์กลางอยู่ที่ Bipolar Junction Transistors (BJTs) เป็นหลัก แต่ก็สามารถสร้างขึ้นได้ดีไม่แพ้กันโดยใช้เทคโนโลยี FET

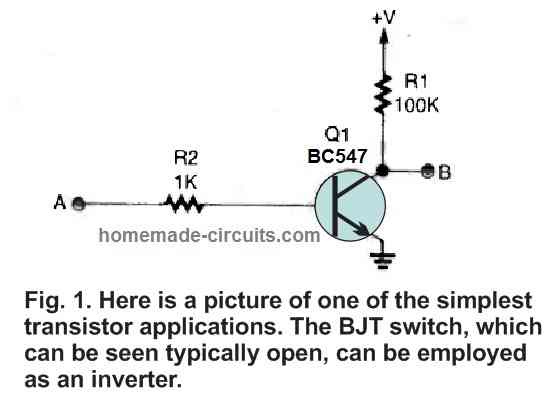

วงจรสวิตช์พื้นฐานเป็นแอปพลิเคชั่นทรานซิสเตอร์อย่างง่าย ซึ่งเป็นหนึ่งในการออกแบบที่ง่ายที่สุด

การทำ NOT Gate ด้วยทรานซิสเตอร์ตัวเดียว

แผนผังของสวิตช์ทรานซิสเตอร์แสดงในรูปที่ 1 ทั้งนี้ขึ้นอยู่กับวิธีการใช้งานในแอปพลิเคชันเฉพาะ สวิตช์อาจถูกมองว่าต่ำหรือเปิดตามปกติ

ลอจิกเกทอินเวอร์เตอร์ NOT เกทแบบธรรมดาสามารถสร้างขึ้นได้โดยวงจรสวิตชิ่งแบบตรงไปตรงมาที่แสดงในรูปที่ 1 (โดยที่จุด A คืออินพุต) เกท NOT ทำงานในลักษณะที่ว่าหากไม่มี DC bias ให้กับฐานของทรานซิสเตอร์ (จุด A; Q1) มันจะยังคงปิดอยู่ ส่งผลให้สูงหรือตรรกะ 1 (เท่ากับระดับ V+) ที่เอาต์พุต ( จุด B)

อย่างไรก็ตาม ทรานซิสเตอร์จะเปิดใช้งานเมื่อมีการให้อคติที่เหมาะสมกับฐานของ Q1 ดันเอาต์พุตของวงจรให้ต่ำหรือไปที่ลอจิก 0 (เกือบเท่ากับศักย์ไฟฟ้าเป็นศูนย์) ทรานซิสเตอร์ที่กำหนด Q1 เป็นทรานซิสเตอร์ไบโพลาร์เอนกประสงค์หรือ BC547 ซึ่งโดยทั่วไปจะใช้ในแอพพลิเคชั่นสวิตช์และแอมพลิฟายเออร์กำลังต่ำ

ทรานซิสเตอร์ใดๆ ที่เทียบเท่ากับมัน (เช่น 2N2222, 2N4401 เป็นต้น) ก็ใช้งานได้ ค่าของ R1 และ R2 ถูกเลือกเพื่อประนีประนอมระหว่างการระบายกระแสไฟต่ำและความเข้ากันได้ ในการออกแบบทั้งหมด ตัวต้านทานทั้งหมดคือ 1/4 วัตต์ 5% หน่วย

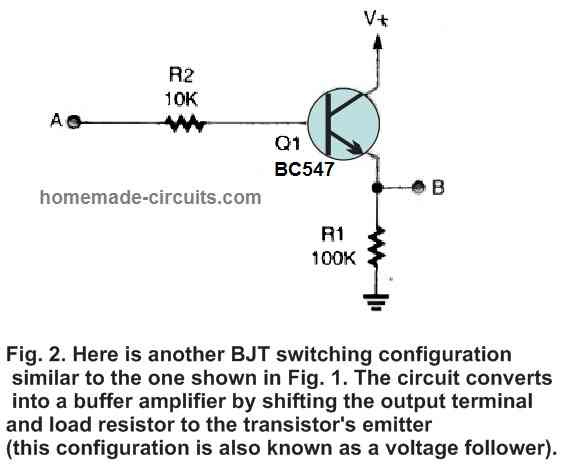

แรงดันไฟฟ้าสามารถปรับได้ระหว่าง 1.4 ถึง 6 โวลต์ DC โปรดทราบว่าวงจรสามารถทำงานได้เหมือนบัฟเฟอร์เมื่อตัวต้านทานโหลดและการเชื่อมต่อเอาต์พุตถูกเลื่อนไปที่ตัวปล่อยของทรานซิสเตอร์

การสร้าง Buffer Gate โดยใช้ BC547 BJT . เดี่ยว

ตัวตามแรงดันไฟฟ้าหรือบัฟเฟอร์แอมพลิฟายเออร์เป็นประเภทของการกำหนดค่าการสลับลอจิกที่เหมือนกับที่แสดงในรูปที่ 2 ควรสังเกตว่าตัวต้านทานโหลดและขั้วเอาต์พุตได้รับการเปลี่ยนจากตัวสะสมของทรานซิสเตอร์ไปเป็นอิมิตเตอร์ในวงจรนี้ ซึ่งก็คือ ความแตกต่างหลักระหว่างการออกแบบนี้กับที่แสดงในรูปที่ 1

การทำงานของทรานซิสเตอร์อาจ 'พลิก' ด้วยการย้ายตัวต้านทานโหลดและขั้วเอาต์พุตไปยังปลายอีกด้านของ BJT

กล่าวอีกนัยหนึ่งเมื่อไม่มีอคติกับอินพุตของวงจร เอาต์พุตของวงจรจะยังคงต่ำ อย่างไรก็ตาม เมื่อมีการจ่ายแรงดันไบแอสที่เพียงพอให้กับอินพุตของวงจร เอาต์พุตของวงจรจะเปลี่ยนสูง (ซึ่งตรงกันข้ามกับสิ่งที่เกิดขึ้นในวงจรก่อนหน้านี้)

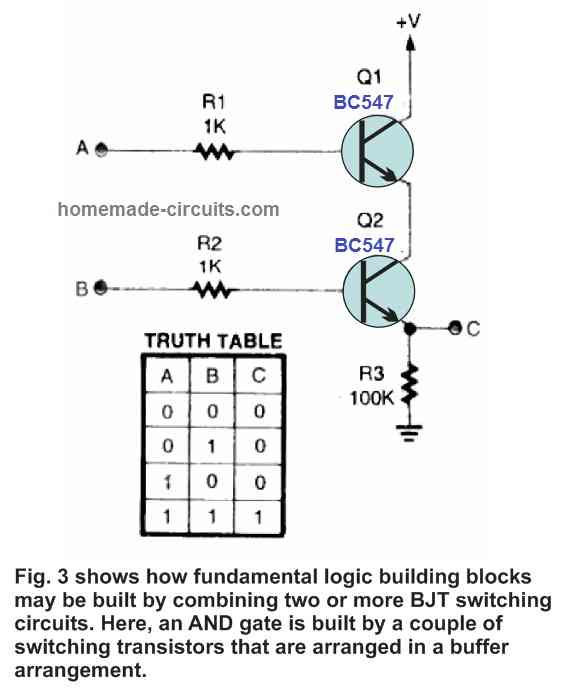

การออกแบบเกทลอจิกสองอินพุตโดยใช้ทรานซิสเตอร์

AND เกทโดยใช้ทรานซิสเตอร์สองตัว

รูปที่ 3 แสดงวิธีการสร้างสองอินพุตและเกตพื้นฐานโดยใช้บัฟเฟอร์คู่พร้อมกับตารางความจริงสำหรับเกตนั้น ตารางความจริงแสดงให้เห็นว่าผลลัพธ์ผลลัพธ์จะเป็นอย่างไรสำหรับชุดอินพุตที่แตกต่างกัน ใช้จุด A และ B เป็นอินพุตของวงจร และจุด C ทำหน้าที่เป็นเอาต์พุตของวงจร

สิ่งสำคัญที่ควรทราบจากตารางความจริงก็คือ พารามิเตอร์อินพุตชุดเดียวส่งผลให้มีสัญญาณเอาต์พุตแบบลอจิกสูง ในขณะที่ชุดค่าผสมอินพุตอื่นๆ ทั้งหมดส่งผลให้เอาต์พุตแบบลอจิกต่ำ เอาต์พุตของเกท AND ในรูปที่ 3 ยังคงต่ำกว่า V+ เล็กน้อยเมื่อเปลี่ยนเป็นสูง

สิ่งนี้เกิดขึ้นเนื่องจากแรงดันตกระหว่างทรานซิสเตอร์สองตัว (Q1 และ Q2)

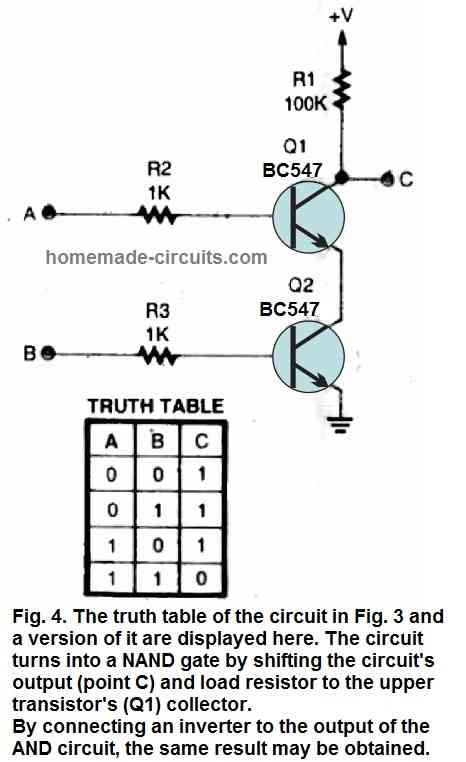

ประตู NAND โดยใช้ทรานซิสเตอร์สองตัว

อีกวงจรหนึ่งของวงจรในรูปที่ 3 และตารางความจริงที่เกี่ยวข้องแสดงไว้ในรูปที่ 4 วงจรจะเปลี่ยนเป็นเกท NAND โดยการขยับเอาต์พุต (จุด C) และตัวต้านทานเอาต์พุตไปยังตัวสะสมทรานซิสเตอร์บน (Q1)

เนื่องจากจำเป็นต้องเปิดทั้ง Q1 และ Q2 เพื่อดึง R1 ด้านต่ำลงกราวด์ การสูญเสียแรงดันไฟฟ้าที่เอาต์พุต C จึงไม่มีความสำคัญ

ถ้าทรานซิสเตอร์ AND หรือทรานซิสเตอร์ NAND เกทต้องการมากกว่าสองอินพุท ทรานซิสเตอร์เพิ่มเติมสามารถเชื่อมต่อได้ดีในแบบที่แสดงเพื่อให้มีสาม สี่ ฯลฯ อินพุต AND หรือ NAND เกท

อย่างไรก็ตาม เพื่อชดเชยการสูญเสียแรงดันไฟของทรานซิสเตอร์แต่ละตัว V+ ควรเพิ่มขึ้นตามลำดับ

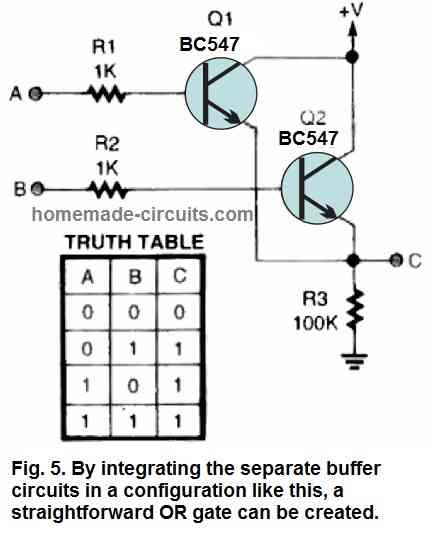

หรือประตูโดยใช้ทรานซิสเตอร์สองตัว

อีกรูปแบบหนึ่งของวงจรลอจิกที่มีสองอินพุตสามารถดูได้ในรูปที่ 5 พร้อมกับตารางความจริงของวงจร OR

เอาต์พุตของวงจรจะสูงเมื่ออินพุต A หรืออินพุต B ถูกผลักให้สูง อย่างไรก็ตาม เนื่องจากทรานซิสเตอร์แบบเรียงซ้อน แรงดันตกคร่อมมากกว่า 0.5 โวลต์ อีกครั้ง ตัวเลขที่แสดงระบุว่ามีแรงดันและกระแสเพียงพอสำหรับการทำงานของประตูทรานซิสเตอร์ที่ตามมา

ประตู NOR ใช้ทรานซิสเตอร์สองตัว

รูปที่ 6 แสดงประตูถัดไปในรายการของเราซึ่งเป็นเกต NOR สองอินพุตพร้อมกับตารางความจริง คล้ายกับวิธีที่เกท AND และ NAND ตอบสนองซึ่งกันและกัน วงจร OR และ NOR ทำเช่นเดียวกัน

แต่ละเกทที่แสดงสามารถจัดหาไดรฟ์ที่เพียงพอเพื่อเปิดใช้งานเกตทรานซิสเตอร์ที่อยู่ติดกันอย่างน้อยหนึ่งตัวหรือมากกว่า

แอปพลิเคชั่นลอจิกเกตทรานซิสเตอร์

คุณจะทำอย่างไรกับวงจรดิจิทัลที่อธิบายข้างต้นที่คุณมีอยู่ในตอนนี้ ทุกสิ่งที่คุณสามารถทำได้ด้วยเกท TTL หรือ CMOS ทั่วไป แต่ไม่ต้องกังวลกับข้อจำกัดด้านแรงดันไฟฟ้า ต่อไปนี้เป็นการประยุกต์ใช้ทรานซิสเตอร์ลอจิกเกทบางส่วน

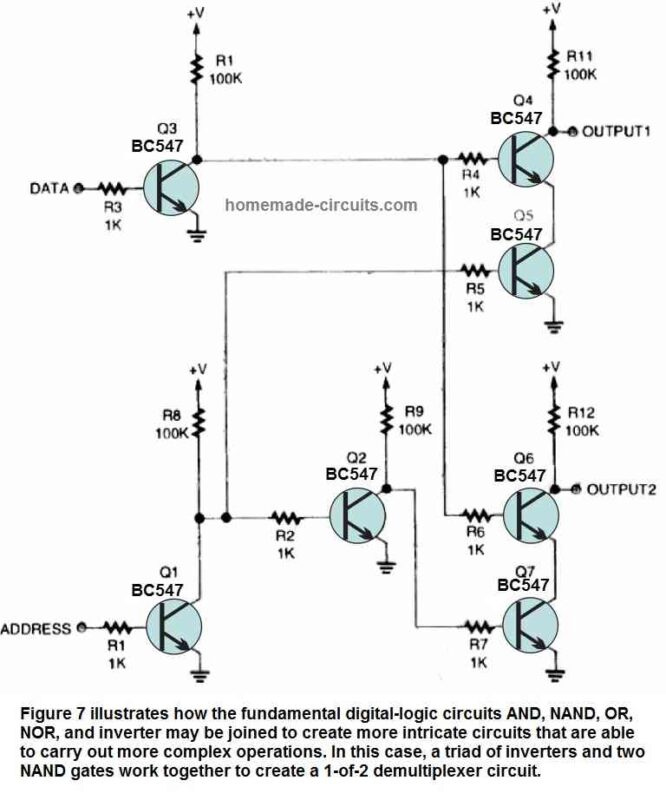

วงจรดีมัลติเพล็กเซอร์

ตัวแยกสัญญาณแบบ 1 ใน 2 ที่มีประตู NOT สามช่องและวงจร NAND สองวงจรแสดงในรูปที่ 7 เอาต์พุตที่เหมาะสมจะถูกเลือกโดยใช้ 'อินพุตที่อยู่' แบบบิตเดียวซึ่งอาจเป็น OUTPUT1 หรือ OUTPUT2 ในขณะที่ข้อมูลการขับขี่ถูกนำไปใช้ ต่อวงจรโดยใช้อินพุต DATA

วงจรจะทำงานได้อย่างมีประสิทธิภาพสูงสุดเมื่ออัตราข้อมูลอยู่ที่ 10 kHz การทำงานของวงจรตรงไปตรงมา อินพุต DATA มาพร้อมกับสัญญาณที่ต้องการ ซึ่งจะเปิด Q3 ON และกลับข้อมูลขาเข้าที่ตัวรวบรวมของ Q3

เอาต์พุตของ Q1 จะเพิ่มขึ้นหากอินพุต ADDRESS ต่ำ (มีการต่อสายดินหรือไม่มีสัญญาณ) ที่ตัวรวบรวมของ Q1 เอาต์พุตสูงแบ่งออกเป็นสองเส้นทาง ในเส้นทางแรก เอาต์พุตของ Q1 จะถูกส่งไปยังฐานของ Q5 (หนึ่งในขาของเกต NAND แบบสองอินพุต) เปิดใช้งานและ 'เปิดใช้งาน' ประตู NAND ที่ประกอบด้วย Q4 และ Q5

ในเส้นทางที่สอง เอาต์พุตสูงของ Q1 จะถูกป้อนเข้าในอินพุตของเกท NOT อีกอัน (Q2) พร้อมกัน หลังจากผ่านการผกผันสองครั้ง เอาต์พุตของ Q2 จะต่ำลง ค่าต่ำสุดนี้มาจากฐานของ Q7 (หนึ่งขั้วของเกต NAND ที่สองซึ่งประกอบด้วย Q6 และ Q7) ดังนั้นจึงปิดวงจร NAND

ข้อมูลหรือสัญญาณใดๆ ที่ใช้กับอินพุต DATA จะมาถึง OUTPUT1 ภายใต้สถานการณ์เหล่านี้ อีกทางหนึ่ง สถานการณ์จะกลับด้านหากได้รับสัญญาณสูงไปยังอินพุต ADDRESS หมายความว่า ข้อมูลใดๆ ที่ให้กับวงจรจะแสดงที่ OUTPUT2 เนื่องจากเกต NAND ของ Q4/Q5 ถูกปิดใช้งาน และเกต NAND ของ Q6/Q7 ถูกเปิดใช้งาน

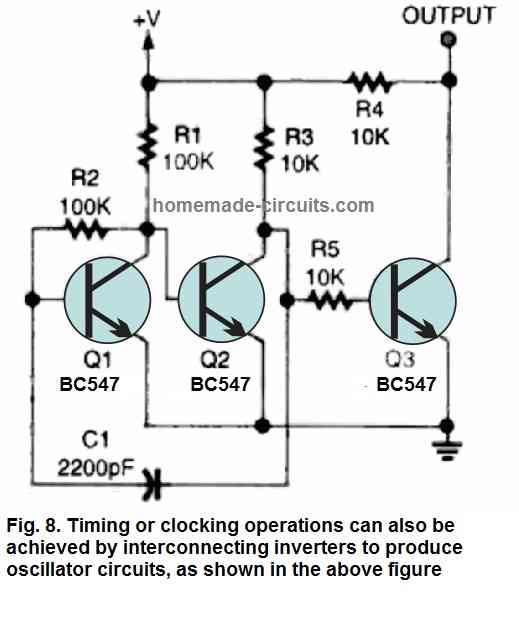

วงจรออสซิลเลเตอร์ (เครื่องกำเนิดนาฬิกา)

แอปพลิเคชั่นลอจิกเกททรานซิสเตอร์ตัวต่อไปของเราที่แสดงในรูปที่ 8 เป็นเครื่องกำเนิดสัญญาณนาฬิกาพื้นฐาน (หรือที่รู้จักในชื่อออสซิลเลเตอร์) ที่ทำจากอินเวอร์เตอร์เกท NOT ธรรมดาสามตัว บริเวณอนาล็อก)

ในการยกกำลังสองเอาต์พุต ให้รวมเกต NOT ตัวที่สาม (Q3) ที่เป็นส่วนเติมเต็มให้กับเอาต์พุตของออสซิลเลเตอร์ ค่า C1 สามารถเพิ่มหรือลดลงเพื่อเปลี่ยนความถี่ในการทำงานของวงจร รูปคลื่นสัญญาณเอาท์พุตมีความถี่ประมาณ 7 kHz โดยมี V+ ที่ 1.5 โวลต์ DC โดยใช้ค่าส่วนประกอบที่ระบุ

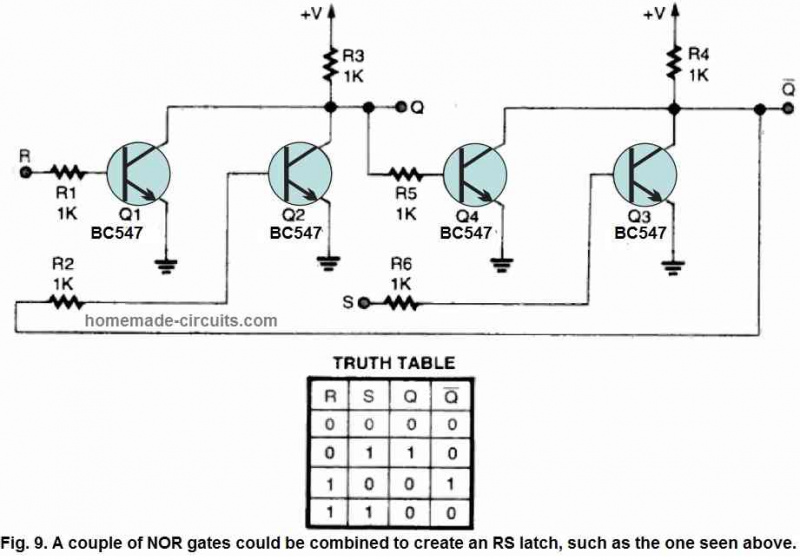

RS Latch Circuit

รูปที่ 9 แสดงวงจรการใช้งานขั้นสุดท้ายของเรา สลัก RS ประกอบด้วยประตู NOR สองช่อง เพื่อให้แน่ใจว่าไดรฟ์เอาท์พุตแข็งแรงที่เอาต์พุต Q และ Q ตัวต้านทาน R3 และ R4 จะถูกปรับเป็น 1k โอห์ม

ตารางความจริงของสลัก RS จะแสดงควบคู่ไปกับการออกแบบแผนผัง เหล่านี้เป็นเพียงตัวอย่างเล็กๆ น้อยๆ ของวงจรลอจิกเกตที่น่าเชื่อถือ แรงดันต่ำ ดิจิตอล ที่อาจสร้างขึ้นโดยใช้ทรานซิสเตอร์แต่ละตัว

วงจรที่ใช้ลอจิกทรานซิสเตอร์ต้องการชิ้นส่วนมากเกินไป

ปัญหามากมายสามารถแก้ไขได้โดยใช้วงจรลอจิกทรานซิสเตอร์แรงดันต่ำเหล่านี้ทั้งหมด อย่างไรก็ตาม การใช้เกททรานซิสเตอร์จำนวนมากเกินไปอาจนำไปสู่ปัญหาใหม่

จำนวนทรานซิสเตอร์และตัวต้านทานอาจเพิ่มขึ้นค่อนข้างมาก หากแอปพลิเคชันที่คุณกำลังสร้างมีเกตจำนวนมาก ซึ่งใช้พื้นที่อันมีค่า

การใช้อาร์เรย์ทรานซิสเตอร์ (ทรานซิสเตอร์จำนวนมากที่หุ้มด้วยพลาสติก) และตัวต้านทาน SIP (แพ็คเกจอินไลน์เดี่ยว) แทนแต่ละยูนิตเป็นวิธีหนึ่งในการแก้ปัญหานี้

วิธีการข้างต้นสามารถประหยัดพื้นที่ได้มากบน pcb ในขณะที่ยังคงประสิทธิภาพให้เท่ากับขนาดเต็มของพวกมัน อาร์เรย์ทรานซิสเตอร์มีให้ในบรรจุภัณฑ์แบบติดตั้งบนพื้นผิว 14 พินผ่านรู และบรรจุภัณฑ์สี่แพ็ค

สำหรับวงจรส่วนใหญ่ ประเภททรานซิสเตอร์ผสมอาจเป็นที่ยอมรับได้ค่อนข้างดี

อย่างไรก็ตาม ขอแนะนำว่าผู้ทดลองทำงานกับทรานซิสเตอร์ประเภทเดียวเพื่อสร้างวงจรลอจิกทรานซิสเตอร์ (หมายความว่าถ้าคุณสร้างส่วนของเกตโดยใช้ BC547 ให้ลองใช้ BJT เดียวกันเพื่อสร้างเกตที่เหลืออื่น ๆ ด้วย)

เหตุผลก็คือว่าทรานซิสเตอร์หลายตัวอาจมีคุณสมบัติแตกต่างกันบ้างและอาจทำงานแตกต่างกัน

ตัวอย่างเช่น สำหรับทรานซิสเตอร์บางตัว ขีดจำกัดของสวิตช์เปิดฐานอาจมากกว่าหรือเล็กกว่าตัวอื่น หรือตัวหนึ่งอาจมีเกนกระแสโดยรวมที่สูงกว่าหรือต่ำกว่าเล็กน้อย

ในทางกลับกัน ค่าใช้จ่ายในการซื้อกล่องขนาดใหญ่ของทรานซิสเตอร์ประเภทเดียวก็อาจต่ำลงเช่นกัน ประสิทธิภาพของวงจรของคุณจะเพิ่มขึ้นหากลอจิกเกตของคุณสร้างขึ้นโดยใช้ทรานซิสเตอร์ที่เข้าชุดกัน และโปรเจ็กต์ทั้งหมดจะคุ้มค่ากว่าในท้ายที่สุด

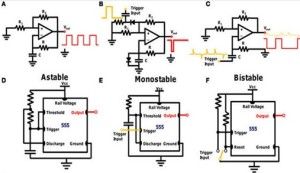

![วงจรตัวบ่งชี้ความดันบรรยากาศ [วงจร LED บารอมิเตอร์]](https://electronics.jf-parede.pt/img/3-phase-power/40/atmospheric-pressure-indicator-circuit-led-barometer-circuit-1.jpg)