JTAG (Joint Test Action Group) เป็นมาตรฐาน IEEE 1149.1 ที่เป็นที่ยอมรับซึ่งพัฒนาขึ้นในปี 1980 เพื่อแก้ปัญหาด้านการผลิตที่เกิดขึ้นภายในบอร์ดอิเล็กทรอนิกส์หรือ แผงวงจรพิมพ์ . เทคโนโลยีนี้ใช้เพื่อให้มีการเข้าถึงการทดสอบเพียงพอสำหรับบอร์ดที่ซับซ้อนแต่ละบอร์ดเมื่อการเข้าถึงการทดสอบลดลง จึงมีการเปิดตัวเทคโนโลยีการสแกนขอบเขต & มาตรฐาน JTAG หรือ ข้อกำหนด JTAG จัดตั้งขึ้น ความซับซ้อนของอุปกรณ์อิเล็กทรอนิกส์เพิ่มขึ้นทุกวัน ดังนั้นข้อกำหนด JTAG จึงกลายเป็นรูปแบบการทดสอบที่ยอมรับในการทดสอบหน่วยอิเล็กทรอนิกส์ที่ซับซ้อนและกะทัดรัด บทความนี้กล่าวถึงภาพรวมของ a JTAG โปรโตคอล – การทำงานกับแอปพลิเคชัน

JTAG คืออะไร?

ชื่อที่กำหนดให้กับ IEEE 1149.1 Standard Test Access Port เช่นเดียวกับ Boundary-Scan Architecture เรียกว่า JTAG (Joint Test Action Group) สถาปัตยกรรมการสแกนขอบเขตนี้ส่วนใหญ่จะใช้ในคอมพิวเตอร์ โปรเซสเซอร์ เพราะโปรเซสเซอร์ตัวแรกที่มี JTAG นั้นออกโดย Intel มาตรฐาน IEEE นี้กำหนดวิธีการทดสอบวงจรของคอมพิวเตอร์เพื่อยืนยันว่าทำงานอย่างถูกต้องหลังจากขั้นตอนการผลิตหรือไม่ บนแผงวงจร จะทำการทดสอบเพื่อตรวจสอบข้อต่อบัดกรี

Joint Test Action Group ให้มุมมองแบบพินเอาต์สำหรับผู้ทดสอบที่มีไอซีแพดทุกตัว ซึ่งช่วยในการระบุความผิดพลาดใดๆ ภายในแผงวงจร เมื่อโปรโตคอลนี้เชื่อมต่อกับชิปแล้ว จะสามารถแนบโพรบเข้ากับชิปได้โดยให้นักพัฒนาสามารถควบคุมชิปได้เช่นเดียวกับการเชื่อมต่อกับชิปอื่นๆ นักพัฒนาสามารถใช้อินเทอร์เฟซกับกลุ่ม Joint Test Action เพื่อคัดลอกเฟิร์มแวร์ไปยังหน่วยความจำแบบไม่ลบเลือนในอุปกรณ์อิเล็กทรอนิกส์

การกำหนดค่า/พินออก

Joint Test Action Group มี 20 พิน โดยแต่ละพินและหน้าที่ของมันจะกล่าวถึงด้านล่าง

Pin1 (VTref): นี่คือพินแรงดันอ้างอิงเป้าหมายที่ใช้เชื่อมต่อกับแหล่งจ่ายไฟหลักของเป้าหมายซึ่งมีช่วงตั้งแต่ 1.5 ถึง 5.0VDC

Pin2 (Vsupply): นี่คือแรงดันไฟจ่ายเป้าหมายที่ใช้เชื่อมต่อแหล่งจ่ายแรงดันไฟหลักของเป้าหมาย 1.5VDC – 5.0VDC

Pin3 (nTRST): นี่คือพินรีเซ็ตการทดสอบที่ใช้เพื่อรีเซ็ตเครื่องสถานะของตัวควบคุม TAP

หมุด (4, 6, 8, 10, 12, 14, 16, 18 & 20): เหล่านี้เป็นหมุด GND ทั่วไป

Pin5 (TDI): นี่คือข้อมูลการทดสอบในพิน ข้อมูลนี้จะถูกย้ายไปยังอุปกรณ์เป้าหมาย ต้องดึงพินนี้ขึ้นตามเงื่อนไขที่กำหนดไว้บนกระดานเป้าหมาย

Pin7 (TMS): นี่คือพินสถานะโหมดการทดสอบที่ถูกดึงเพื่อกำหนดเงื่อนไขถัดไปของเครื่องสถานะของตัวควบคุม TAP

Pin9 (TCK): นี่คือพินนาฬิกาทดสอบที่ซิงโครไนซ์การทำงานของเครื่องสถานะภายในในตัวควบคุม TAP

Pin11 (RTCK): นี่คือพิน Input Return TCK ที่ใช้ในอุปกรณ์ที่รองรับการตอกบัตรแบบปรับได้

Pin13 (TDO): นี่คือพิน Test Data Out ดังนั้นข้อมูลจะถูกย้ายออกจากอุปกรณ์เป้าหมายไปยัง Flyswatter

Pin15 (nSRST): นี่คือพินรีเซ็ตระบบเป้าหมายซึ่งเชื่อมต่อกับสัญญาณรีเซ็ตหลักของเป้าหมาย

หมุด 17 & 19 (NC): สิ่งเหล่านี้ไม่ใช่พินที่เชื่อมต่อ

JTAG ทำงาน

การใช้งานดั้งเดิมของ JTAG มีไว้สำหรับการทดสอบขอบเขต นี่คือแผงวงจรพิมพ์อย่างง่ายที่มีไอซีสองตัวเช่น CPU & FPGA . บอร์ดทั่วไปอาจมีไอซีหลายตัว โดยทั่วไป ไอซีจะประกอบด้วยพินจำนวนมากที่ต่อร่วมกับจุดเชื่อมต่อจำนวนมาก ในไดอะแกรมต่อไปนี้ แสดงการเชื่อมต่อสี่รายการเท่านั้น

ดังนั้นหากคุณออกแบบบอร์ดหลายๆ บอร์ดโดยที่ทุกๆ บอร์ดจะมีการเชื่อมต่อนับพัน ในนั้นมีบางกระดานที่ไม่ดี ดังนั้นเราต้องตรวจสอบว่าบอร์ดใดใช้งานได้และบอร์ดใดไม่ทำงาน ด้วยเหตุนี้จึงได้ออกแบบ Joint Test Action Group

โปรโตคอลนี้สามารถใช้พินควบคุมของชิปทั้งหมดได้ แต่ในแผนภาพต่อไปนี้ Joint Test Action Group จะสร้างพินเอาต์พุตทั้งหมดของ CPU และพินอินพุตทั้งหมดของ FPGA หลังจากนั้น โดยการส่งข้อมูลจำนวนหนึ่งจากพินของ CPU และการอ่านค่าของพินจาก FPGA ทำให้ JTAG ระบุว่าการเชื่อมต่อของบอร์ด PCB นั้นใช้ได้

ที่จริงแล้ว Joint Test Action Group มีสี่สัญญาณลอจิก TDI, TDO, TMS & TCK และสัญญาณเหล่านี้จำเป็นต้องเชื่อมต่อในลักษณะเฉพาะ ในตอนแรก TMS & TCK เชื่อมต่อแบบขนานกับ IC ทั้งหมดของ JTAG

หลังจากนั้น ทั้ง TDI และ TDO จะเชื่อมต่อกันเพื่อสร้างห่วงโซ่ ดังที่คุณสังเกตได้ IC ที่สอดคล้องกับ JTAG ทุกตัวจะมี 4 พินซึ่งใช้สำหรับ JTAG โดยที่ 3 พินเป็นอินพุตและเอาต์พุตพินที่ 4 พินที่ห้าเช่น TRST เป็นตัวเลือก โดยปกติแล้ว หมุด JTAG จะไม่ถูกแชร์เพื่อวัตถุประสงค์อื่น

ด้วยการใช้ Joint Test Action Group ไอซีทั้งหมดใช้การทดสอบขอบเขตซึ่ง JTAG ได้สร้างเหตุผลดั้งเดิมขึ้น ในปัจจุบัน มีการใช้โปรโตคอลนี้เพื่ออนุญาตสิ่งต่าง ๆ เช่น การกำหนดค่า FPGA และหลังจากนั้นจะใช้ JTAG ในแกน FPGA เพื่อจุดประสงค์ในการดีบัก

สถาปัตยกรรม JTAG

สถาปัตยกรรม JTAG แสดงอยู่ด้านล่าง ในสถาปัตยกรรมนี้ สัญญาณทั้งหมดระหว่างตรรกะหลักของอุปกรณ์และพินจะถูกขัดจังหวะผ่านพาธการสแกนแบบอนุกรมที่เรียกว่า BSR หรือ Boundary Scan Register BSR นี้รวมถึง 'เซลล์' การสแกนขอบเขตต่างๆ โดยทั่วไป เซลล์สแกนขอบเขตเหล่านี้จะมองไม่เห็น แต่สามารถใช้เพื่อตั้งค่าหรืออ่านค่าภายในโหมดทดสอบจากหมุดของอุปกรณ์ได้

อินเทอร์เฟซ JTAG ที่เรียกว่า TAP หรือ Test Access Port ใช้สัญญาณที่แตกต่างกันเพื่อรองรับการดำเนินการสแกนขอบเขต เช่น TCK, TMS, TDI, TDO และ TRST

- สัญญาณ TCK หรือนาฬิกาทดสอบจะซิงโครไนซ์การทำงานภายในของเครื่องสถานะ

- สัญญาณ TMS หรือ Test Mode Select จะถูกสุ่มตัวอย่างที่ขอบที่เพิ่มขึ้นของสัญญาณนาฬิกาทดสอบเพื่อตัดสินสถานะถัดไป

- สัญญาณ TDI หรือ Test Data In หมายถึงข้อมูลที่เลื่อนไปยังอุปกรณ์ทดสอบ มิฉะนั้น ตรรกะในการเขียนโปรแกรม เมื่อเครื่องสถานะภายในอยู่ในสถานะที่ถูกต้องแล้ว จะมีการสุ่มตัวอย่างที่ขอบที่เพิ่มขึ้นของ TCK

- สัญญาณ TDO หรือ Test Data Out หมายถึงข้อมูลที่เลื่อนออกไปของอุปกรณ์ทดสอบหรือตรรกะการเขียนโปรแกรม เมื่อเครื่องสถานะภายในอยู่ในสถานะที่ถูกต้องแล้วจะมีผลใช้ได้ที่ขอบที่ลดลงของTCK

- TRST หรือ Test Reset เป็นพินเสริมที่ใช้ในการรีเซ็ตเครื่องสถานะของตัวควบคุม TAP

TAP Controller

จุดเชื่อมต่อทดสอบในสถาปัตยกรรมของ JTAG ประกอบด้วยตัวควบคุม TAP การลงทะเบียนคำสั่ง และการลงทะเบียนข้อมูลการทดสอบ ตัวควบคุมนี้มีเครื่องสถานะการทดสอบซึ่งมีหน้าที่ในการอ่านสัญญาณ TMS & TCK ที่นี่ data i/p pin ใช้เพื่อโหลดข้อมูลลงในเซลล์ขอบเขตระหว่างแกนหลักของ IC และพินทางกายภาพ และยังโหลดข้อมูลลงในการลงทะเบียนข้อมูลตัวใดตัวหนึ่งหรือในการลงทะเบียนคำสั่ง data o/p pin ใช้สำหรับอ่านข้อมูลจากรีจิสเตอร์หรือเซลล์ขอบเขต

เครื่องสถานะของตัวควบคุม TAP ถูกควบคุมโดย TMS และมีการโอเวอร์คล็อกโดย TCK เครื่องสถานะใช้สองเส้นทางสำหรับแสดงสองโหมดที่แตกต่างกันเช่นโหมดคำสั่งและโหมดข้อมูล

ทะเบียน

มีการลงทะเบียนสองประเภทภายในการสแกนขอบเขต อุปกรณ์ที่สอดคล้องทุกเครื่องมีการลงทะเบียนข้อมูลอย่างน้อยสองรายการขึ้นไปและการลงทะเบียนคำสั่งหนึ่งรายการ

คำสั่งลงทะเบียน

การลงทะเบียนคำสั่งใช้เพื่อเก็บคำสั่งปัจจุบัน ดังนั้นข้อมูลจึงถูกใช้โดยตัวควบคุม TAP เพื่อตัดสินใจว่าจะดำเนินการใดกับสัญญาณที่ได้รับ โดยส่วนใหญ่ ข้อมูลการลงทะเบียนคำสั่งจะอธิบายว่าสัญญาณการลงทะเบียนข้อมูลใดต้องถูกส่งผ่าน

การลงทะเบียนข้อมูล

การลงทะเบียนข้อมูลมีให้เลือกสามประเภท ได้แก่ BSR (Boundary Scan Register), BYPASS และ ID CODES register และอาจมีการลงทะเบียนข้อมูลอื่น ๆ แต่ไม่จำเป็นว่าเป็นองค์ประกอบของมาตรฐาน JTAG

ทะเบียนสแกนขอบเขต (BSR)

BSR คือการลงทะเบียนข้อมูลการทดสอบหลักที่ใช้ในการเปลี่ยนข้อมูลจากและไปยังพิน I/O ของอุปกรณ์

บายพาส

บายพาสคือการลงทะเบียนแบบบิตเดียวที่ใช้ในการส่งผ่านข้อมูลจาก TDI – TDO ดังนั้นจึงอนุญาตให้ทดสอบอุปกรณ์เพิ่มเติมภายในวงจรโดยใช้ค่าโสหุ้ยขั้นต่ำ

รหัสประจำตัว

การลงทะเบียนข้อมูลประเภทนี้ประกอบด้วยรหัสประจำตัวและหมายเลขรุ่นแก้ไขสำหรับอุปกรณ์ ดังนั้นข้อมูลนี้จึงทำให้อุปกรณ์สามารถเชื่อมต่อกับไฟล์ BSDL (ภาษาคำอธิบายการสแกนขอบเขต) ไฟล์นี้มีรายละเอียดการกำหนดค่า Boundary Scan สำหรับอุปกรณ์

การทำงานของ JTAG คือในขั้นต้น โหมดคำสั่งจะถูกเลือกโดยที่สถานะใดสถานะหนึ่งใน 'เส้นทาง' ของโหมดนี้ อนุญาตให้ผู้ปฏิบัติงานนาฬิกาภายในคำสั่งโดย TDI หลังจากนั้นเครื่องของรัฐจะพัฒนาจนกว่าจะมีการจัดเรียงใหม่ ขั้นตอนต่อไปสำหรับคำแนะนำส่วนใหญ่คือการเลือกโหมดข้อมูล ดังนั้นในโหมดนี้ ข้อมูลจะถูกโหลดผ่าน TDI เพื่ออ่านจาก TDO สำหรับ TDI & TDO เส้นทางข้อมูลจะถูกจัดเรียงตามคำสั่งที่ได้รับการโอเวอร์คล็อก เมื่อการดำเนินการอ่าน/เขียนเสร็จสิ้น เครื่องสถานะจะพัฒนาเป็นสถานะรีเซ็ตอีกครั้ง

ความแตกต่างระหว่าง JTAG กับ UART

ความแตกต่างระหว่าง JTAG และ UART มีดังต่อไปนี้

| JTAG |

UART |

| คำว่า 'JTAG' ย่อมาจาก Joint Test Action Group | คำว่า “ UART ” ย่อมาจาก Universal Asynchronous Receiver/Transmitter |

| มันเป็นอินเทอร์เฟซแบบซิงโครนัสที่ใช้ฮาร์ดแวร์ในตัวสำหรับการเขียนโปรแกรมแฟลช . | UART เป็นอินเทอร์เฟซแบบอะซิงโครนัสที่ใช้ bootloader ที่ทำงานภายในหน่วยความจำ |

| เป็นชุดของพอร์ตทดสอบที่ใช้สำหรับการดีบัก แต่ยังสามารถใช้ในการเขียนโปรแกรมเฟิร์มแวร์

|

UART เป็นชิปประเภทหนึ่งที่ควบคุมการสื่อสารไปและกลับจากอุปกรณ์ เช่น ไมโครคอนโทรลเลอร์, ROM, RAM เป็นต้น ส่วนใหญ่แล้วจะเป็นการเชื่อมต่อแบบอนุกรมที่ช่วยให้เราสื่อสารกับอุปกรณ์ได้ |

| มีอยู่ในสี่ประเภท TDI, TDO, TCK, TMS & TRST | มีให้เลือก 2 แบบคือ UART & FIFO UART |

| Joint Test Action Group คือการเขียนโปรแกรมแบบอนุกรมหรือโปรโตคอลการเข้าถึงข้อมูลที่ใช้ในการเชื่อมต่อไมโครคอนโทรลเลอร์และอุปกรณ์ที่เกี่ยวข้อง | UART เป็นชิปชนิดหนึ่ง มิฉะนั้นจะเป็นส่วนประกอบย่อยของไมโครคอนโทรลเลอร์ ซึ่งใช้เพื่อจัดเตรียมฮาร์ดแวร์สำหรับสร้างสตรีมอนุกรมแบบอะซิงโครนัส เช่น RS-232/RS-485 |

| ส่วนประกอบ JTAG คือโปรเซสเซอร์, FPGA, CPLDs , เป็นต้น | ส่วนประกอบ UART ได้แก่ ตัวสร้าง CLK, รีจิสเตอร์ I/O shift, ส่งหรือรับบัฟเฟอร์, บัฟเฟอร์บัสข้อมูลระบบ, ลอจิกควบคุมการอ่านหรือเขียน ฯลฯ |

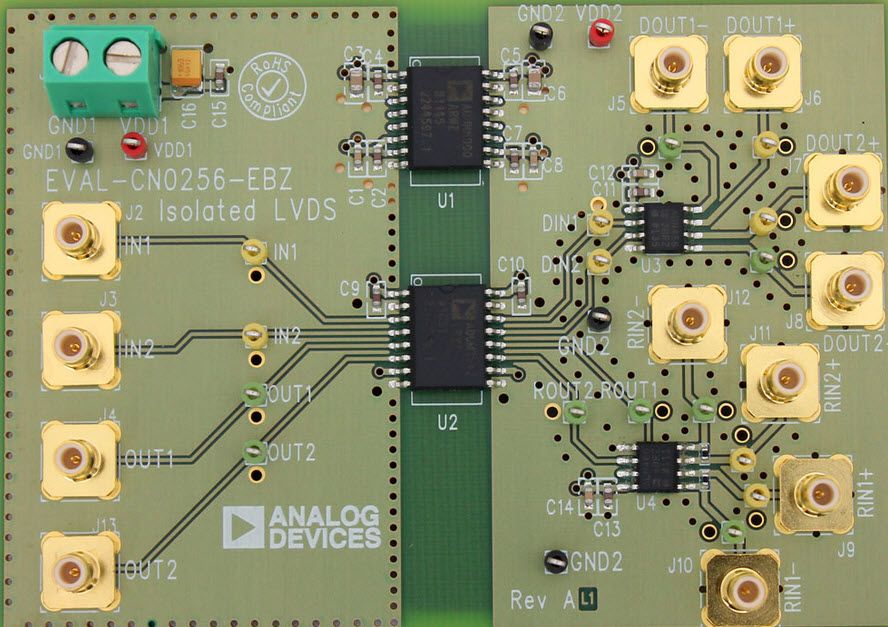

ตัววิเคราะห์โปรโตคอล JTAG

JTAG Protocol Analyzer เช่น PGY-JTAG-EX-PD เป็น Protocol Analyzer ประเภทหนึ่งซึ่งรวมถึงคุณลักษณะบางอย่างในการจับภาพและแก้ปัญหาการสื่อสารระหว่างโฮสต์และการออกแบบภายใต้การทดสอบ เครื่องวิเคราะห์ประเภทนี้เป็นเครื่องมือชั้นนำที่ช่วยให้วิศวกรทดสอบและออกแบบสามารถทดสอบการออกแบบเฉพาะของ JTAG สำหรับข้อมูลจำเพาะผ่านการจัดเรียง PGY-JTAG-EX-PD เช่น Master หรือ Slave เพื่อสร้างทราฟฟิก JTAG และถอดรหัสแพ็กเก็ตถอดรหัสของ โปรโตคอลกลุ่มการดำเนินการทดสอบร่วม

คุณสมบัติ

คุณสมบัติของตัววิเคราะห์โปรโตคอล JTAG มีดังต่อไปนี้

- รองรับความถี่ JTAG สูงสุด 25MH

- มันสร้างทราฟฟิก JTAG & ถอดรหัสโปรโตคอลสำหรับบัสพร้อมกัน

- มีความสามารถ JTAG Master

- ตัวแปรความเร็วข้อมูล JTAG และรอบการทำงาน

- TDI & TCK ที่ผู้ใช้กำหนด

- โฮสต์คอมพิวเตอร์อินเทอร์เฟซ USB 2.0 หรือ 3.0

- การวิเคราะห์ข้อผิดพลาดภายใน Protocol Decode

- แผนภาพเวลาบัสถอดรหัสโปรโตคอล

- ข้อมูลโปรโตคอลต่อเนื่องที่สตรีมไปยังโฮสต์คอมพิวเตอร์เพื่อให้มีบัฟเฟอร์ขนาดใหญ่

- รายการกิจกรรมโปรโตคอล

- ที่ความเร็วต่างๆ สคริปต์การออกกำลังกายสามารถเขียนเพื่อรวมการสร้าง data frame หลายตัวเข้าด้วยกัน

ไดอะแกรมกำหนดเวลา

ดิ แผนภาพเวลาของ JTAG โปรโตคอลแสดงอยู่ด้านล่าง ในแผนภาพต่อไปนี้ พิน TDO ยังคงอยู่ในสภาวะอิมพีแดนซ์สูง ยกเว้นในระหว่างสถานะตัวควบคุม shift-IR/ shift-DR

ในเงื่อนไขตัวควบคุม shift-IR & Shift-DR พิน TDO จะได้รับการอัปเดตบนขอบที่ลดลงของ TCK ผ่าน Target และสุ่มตัวอย่างบนขอบที่เพิ่มขึ้นของ TCK ผ่าน Host

หมุด TDI และ TMS ทั้ง 2 ตัวนั้นถูกสุ่มตัวอย่างบนขอบที่เพิ่มขึ้นของ TCK ผ่าน Target อัปเดตบนขอบที่ลดลงมิฉะนั้น TCK ผ่าน Host

แอปพลิเคชั่น

ดิ แอปพลิเคชัน JTAG รวมสิ่งต่อไปนี้

- Joint Test Action Group มักใช้ในโปรเซสเซอร์เพื่อให้สิทธิ์ในการเข้าสู่ฟังก์ชันการจำลองหรือแก้ไขจุดบกพร่อง

- CPLD และ FPGA ทั้งหมดใช้สิ่งนี้เป็นอินเทอร์เฟซเพื่อให้สามารถเข้าถึงฟังก์ชันการเขียนโปรแกรมได้

- ใช้สำหรับการทดสอบ PCB โดยไม่มีการเข้าถึงทางกายภาพ

- ใช้สำหรับการทดสอบการผลิตระดับบอร์ด

ดังนั้น ทั้งหมดนี้เกี่ยวกับ ภาพรวมของ JTAG – การกำหนดค่าพิน ทำงานกับแอปพลิเคชัน JTAG มาตรฐานอุตสาหกรรมใช้สำหรับการตรวจสอบการออกแบบและการทดสอบ PCB หลังการผลิต นี่คือคำถามสำหรับคุณ JTAG ย่อมาจาก?