คำว่า VLSI ย่อมาจาก“ Very Large Scale Integration Technology” ซึ่งเกี่ยวข้องกับการออกแบบวงจรรวม (ICs) โดยการรวมหลายพัน ทรานซิสเตอร์ อย่างมีเหตุผลลงในชิปตัวเดียวโดย วงจรลอจิกที่แตกต่างกัน . ในที่สุด IC เหล่านี้จะลดพื้นที่วงจรที่ถูกครอบครองเมื่อเปรียบเทียบกับวงจรที่มี IC ทั่วไป พลังการคำนวณและการใช้พื้นที่เป็นความท้าทายหลักของการออกแบบ VLSI การดำเนินโครงการ VLSI เป็นการเปิดอาชีพที่ท้าทายและสดใสสำหรับนักศึกษาตลอดจนนักวิจัย พื้นที่แนวโน้มใหม่ของ VLSI คือ อาร์เรย์เกทที่ตั้งโปรแกรมฟิลด์ได้ แอปพลิเคชัน (FPGA) การออกแบบ ASIC และ SOC รายชื่อโครงการ VLSI บางส่วนมีให้ด้านล่างสำหรับนักเรียนที่กำลังมองหาโครงการในสาขานี้อย่างจริงจัง บทความนี้กล่าวถึงภาพรวมของโครงการ VLSI ตาม FPGA, Xilinx, IEEE, Mini, Matlab และอื่น ๆ ตามรายการด้านล่าง โครงการเหล่านี้มีประโยชน์มากสำหรับนักศึกษาวิศวกรรมศาสตร์นักศึกษา M.tech

โครงการ VLSI สำหรับนักศึกษาวิศวกรรม

โครงการ VLSI พร้อมบทคัดย่อสำหรับนักศึกษาวิศวกรรมอิเล็กทรอนิกส์จะกล่าวถึงด้านล่าง

โครงการ VLSI

1). การเปลี่ยนแปลงของ Wavelet แบบไม่ต่อเนื่องโดยใช้ 3D Lifting

โครงการนี้ช่วยในการให้ภาพที่มีความแม่นยำสูงโดยใช้การเข้ารหัสของรูปภาพโดยไม่สูญเสียข้อมูล เพื่อให้บรรลุสิ่งนี้กระบวนการนี้ใช้ตัวกรองการยกขึ้นอยู่กับการเปลี่ยนแปลงของสถาปัตยกรรม VLSI เวฟเล็ตแบบแยก 3 มิติ

2). การออกแบบตัวคูณ SFQ 4 บิตด้วยฮาร์ดแวร์ความเร็วสูงอย่างมีประสิทธิภาพ

โครงการนี้ส่วนใหญ่จะใช้สำหรับการใช้ตัวเข้ารหัสบูธที่แก้ไข (MBE) ที่ใช้ SFQ แบบ 4 บิต ตัวคูณ . ตัวคูณนี้ให้ประสิทธิภาพที่ดีเมื่อเทียบกับตัวเข้ารหัสบูธทั่วไป โครงการนี้ส่วนใหญ่จะใช้ในการประยุกต์ใช้การหน่วงเวลาวิกฤต

3). โปรเซสเซอร์การเข้ารหัสที่ใช้ในสมาร์ทการ์ดที่มีพื้นที่ที่มีประสิทธิภาพ

โครงการนี้ใช้เพื่อใช้อัลกอริทึมการเข้ารหัสสามแบบที่รองรับทั้งคีย์ส่วนตัวและคีย์สาธารณะที่ใช้ใน สมาร์ทการ์ด แอปพลิเคชั่นสำหรับการตรวจสอบผู้ใช้และข้อมูลที่ปลอดภัยอย่างยิ่ง การสื่อสาร .

4). ตัวคูณความเร็วสูงหรือพลังงานต่ำพร้อมวิธีการปราบปรามอำนาจปลอม

ระบบที่นำเสนอนี้จะกรองสัญญาณเท็จที่ไร้ประโยชน์ของหน่วยเลขคณิตเพื่อหลีกเลี่ยงการส่งข้อมูลที่ไม่จำเป็นซึ่งไม่มีผลต่อผลการคำนวณล่าสุด ระบบนี้ใช้วิธี SPST สำหรับตัวคูณเพื่อให้ได้พลังงานต่ำและการส่งข้อมูลความเร็วสูง

5). การบีบอัดและการบีบอัดอัลกอริทึมข้อมูลแบบไม่สูญเสียข้อมูล

โครงการนี้ใช้สำหรับสถาปัตยกรรมฮาร์ดแวร์ 2 ขั้นตอนเป็นหลักโดยขึ้นอยู่กับคุณสมบัติอัลกอริทึม PDLZW (Parallel Dictionary LZW) รวมถึงอัลกอริทึมประเภท Adaptive Huffman ซึ่งใช้สำหรับทั้งแอปพลิเคชันของการบีบอัดข้อมูลแบบไม่สูญเสียและการคลายการบีบอัดแบบไม่สูญเสีย

6). สถาปัตยกรรมของตัวถอดรหัสเทอร์โบที่มีความซับซ้อนต่ำสำหรับ WSN ที่ประหยัดพลังงาน

ระบบที่นำเสนอนี้ใช้เพื่อลดการใช้พลังงานทั้งหมดตลอดการส่งข้อมูลของ WSN ผ่านอัลกอริธึมการสลายตัวของ LUT-Log-BCJR ไปสู่การดำเนินการ ACS พื้นฐาน (เพิ่มการเปรียบเทียบเลือก)

7). สถาปัตยกรรม VLSI สำหรับการลบ Impulse Noise ของภาพอย่างมีประสิทธิภาพ

ระบบที่นำเสนอนี้ส่วนใหญ่ใช้เพื่อปรับปรุงคุณภาพของภาพที่มองเห็นเพื่อหลีกเลี่ยงโอกาสที่จะเกิดความเสียหายจากสัญญาณรบกวนอิมพัลส์เพื่อใช้สถาปัตยกรรม VLSI ที่มีประสิทธิภาพโดยใช้ฟิลเตอร์ถนอมขอบ

8). สถาปัตยกรรมของโปรเซสเซอร์ในหน่วยความจำที่ใช้สำหรับการบีบอัดมัลติมีเดีย

ระบบที่นำเสนอนี้มีสถาปัตยกรรมที่มีความซับซ้อนต่ำสำหรับไฟล์ โปรเซสเซอร์ ในหน่วยความจำเพื่อรองรับการใช้งานมัลติมีเดียเช่นการบีบอัดภาพวิดีโอผ่านการใช้คำสั่งเดี่ยวขนาดใหญ่แนวคิดข้อมูลหลายคำและคำสั่ง

9). เทคนิคการซิงโครไนซ์เวลาด้วยอัตราสัญลักษณ์สำหรับระบบ OFDM ไร้สายที่ใช้พลังงานต่ำ

ระบบที่นำเสนอนี้ส่วนใหญ่ใช้เพื่อปรับปรุงการทำงานของ OFDM แบบไร้สาย (Orthogonal Frequency Division มัลติเพล็กซ์ ) ผ่านการลดกำลังของเบสแบนด์ทั้งหมดด้วยความช่วยเหลือของนาฬิกา เครื่องกำเนิดไฟฟ้า ด้วยเฟสที่ปรับได้และตัวควบคุมเวลาตัวอย่างแบบไดนามิก

10). แอคคูมูเลเตอร์ที่ใช้พลังงานต่ำและการใช้งานตัวคูณความเร็วสูงด้วย SPST Adder & Verilog

โครงการนี้ใช้ในการออกแบบ MAC ที่ใช้พลังงานต่ำและความเร็วสูง (ตัวคูณและตัวสะสม) ผ่านการยอมรับวิธีการปราบปรามที่ผิดพลาดของพลังงานบน MBE (ตัวเข้ารหัสบูธที่แก้ไข) ด้วยการใช้การออกแบบนี้สามารถหลีกเลี่ยงการกระจายพลังงานของสวิตช์ทั้งหมดได้

11). การออกแบบและการใช้งานตัวประมวลผลหุ่นยนต์โดยการเปิดใช้งานการป้องกันการชนกันด้วยเทคโนโลยี RFID

ระบบที่นำเสนอส่วนใหญ่จะใช้เพื่อใช้โปรเซสเซอร์หุ่นยนต์ที่มีระบบป้องกันการชนกันเพื่อหลีกเลี่ยงการชนกันทางกายภาพของหุ่นยนต์ในสภาพแวดล้อมของหุ่นยนต์หลายตัว อัลกอริทึมนี้ส่วนใหญ่ใช้งานโดยใช้เทคโนโลยี VHDL & RFID

12). การออกแบบวงจรลอจิกแบบประหยัดพลังงานโดยใช้วิธีอะเดียแบติก

ระบบนี้แสดงให้เห็นถึงการออกแบบวงจรลอจิกโดยใช้วิธีอะเดียแบติกอย่างมีประสิทธิภาพเมื่อเปรียบเทียบกับการออกแบบ CMOS แบบเดิมด้วยความช่วยเหลือของวงจรโดยใช้ ประตู NAND & NOR . ด้วยการใช้วิธีอะเดียแบติกการกระจายพลังงานภายในเครือข่ายสามารถลดลงได้เช่นเดียวกับการรีไซเคิลพลังงานที่เก็บไว้ภายในตัวเก็บประจุโหลด

3). ระบบเข้ารหัสเพื่อเพิ่มความเร็วในการประมวลผลของระบบ

ความตั้งใจหลักของโครงการนี้คือการเพิ่มความปลอดภัยในการรับส่งข้อมูลเพื่อปรับปรุงความเร็วของการประมวลผลโดยใช้อัลกอริทึมของ AES โดยใช้ FPGA ดังนั้นการจำลองนี้รวมถึงการออกแบบทางคณิตศาสตร์สามารถทำได้ด้วยความช่วยเหลือของรหัส VHDL

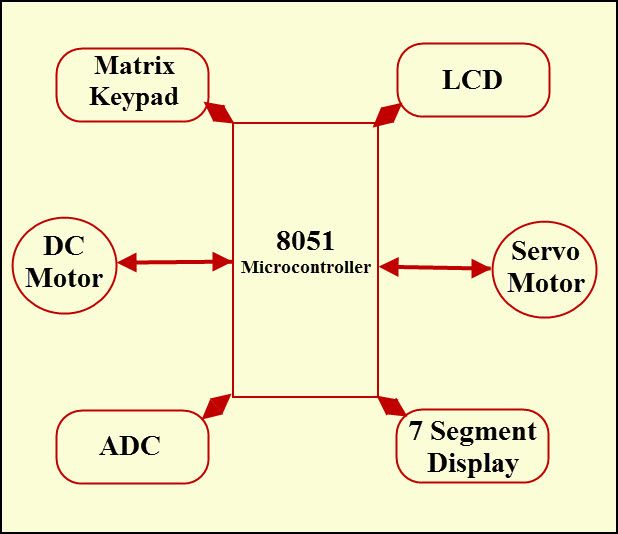

14). IP Block ของ AHM หรือ Advanced High-Performance Bus

โครงการนี้ส่วนใหญ่ใช้ในการออกแบบสถาปัตยกรรมขั้นสูง ไมโครคอนโทรลเลอร์ Bus (AMB) โดยใช้ AHBN (Advanced High-Performance Bus) โครงการนี้สามารถออกแบบด้วยโค้ด VHDL โดยใช้บล็อกเช่น master & save

15). เครื่องรับส่งสัญญาณ RF แบบหลายโหมดที่ใช้ DSM พร้อมหลายช่องสัญญาณ

ระบบนี้ส่วนใหญ่ใช้ในการออกแบบสถาปัตยกรรมตัวส่งและตัวรับสัญญาณแบบมัลติและ RF หลายช่องสัญญาณพร้อมโมดูเลเตอร์ Delta-Sigma ระบบที่นำเสนอนี้ใช้ภาษา VHDL เพื่อใช้สถาปัตยกรรมสองแบบ

16). Concentrator ของ Knockout Switch โดยใช้ Asynchronous Transfer Mode

ด้วยการใช้โปรเจ็กต์นี้สามารถออกแบบสวิตช์ที่น่าพิศวงตามการถ่ายโอนแบบอะซิงโครนัสได้ด้วยความช่วยเหลือของเครื่องมือเช่น VHS & VHDL สวิตช์น็อคเอาต์นี้สามารถใช้ในเครือข่ายของแพ็กเก็ตวงจรเสมือนเช่นเดียวกับการใช้งานของดาตาแกรม

17). วงจรอะซิงโครนัสการสังเคราะห์ตามพฤติกรรม

โครงการนี้ส่วนใหญ่ใช้เพื่อจัดหาเทคนิคการสังเคราะห์เชิงพฤติกรรมที่ใช้สำหรับวงจรอะซิงโครนัส ทั้งเทมเพลตเช่น balsa และการใช้งานแบบอะซิงโครนัสเป็นองค์ประกอบหลักในการออกแบบ

18). การออกแบบ AMBA โดยใช้ตัวควบคุมหน่วยความจำที่รองรับของ AHB

โครงการนี้ใช้ในการออกแบบ MC (ตัวควบคุมหน่วยความจำ) โดยขึ้นอยู่กับ AMBA (Advanced Microcontroller Bus Architecture) สำหรับการควบคุมหน่วยความจำระบบโดยใช้หน่วยความจำหลักเช่น SRAM & ROM

19). ดำเนินการติดตั้ง Tree Adder

Carry Tree Adder ตามการออกแบบ VLSI เรียกว่าเป็นตัวเพิ่มประสิทธิภาพที่ดีที่สุดเมื่อเทียบกับตัวเพิ่มไบนารีตามปกติ ส่วนเสริมที่ดำเนินการโดยโครงการนี้ ได้แก่ ต้นไม้ที่ประกอบไปด้วยหินโกเงะและหินโกเกจกระจัดกระจาย

20). การออกแบบคอร์ดิคตามการหมุนของมุมคงที่

แนวคิดหลักของระบบที่นำเสนอนี้คือการเปลี่ยนเวกเตอร์โดยใช้มุมคงที่ มุมเหล่านี้จำเป็นสำหรับเกมหุ่นยนต์ การประมวลผลภาพ ฯลฯ โดยการใช้โครงงานนี้การหมุนเวกเตอร์สามารถทำได้โดยใช้มุมเฉพาะโดยการออกแบบของ CORDIC (คอมพิวเตอร์ดิจิตอลการหมุนพิกัด)

21). การออกแบบตัวกรอง FIR พร้อมเลขคณิตแบบกระจายของตารางการค้นหา

ระบบที่นำเสนอนี้ส่วนใหญ่ช่วยเพิ่ม ฟิลเตอร์ FIR ประสิทธิภาพโดยการออกแบบโดยใช้เลขคณิตแบบกระจายของตารางค้นหา 3 มิติแทนตัวคูณ ดังนั้นการออกแบบนี้สามารถใช้งานได้โดยใช้โปรแกรมเช่น FPGA & Xilinx

22). Push-Pull Pulsed Latches พร้อมเงื่อนไขความเร็วสูงและพลังงานต่ำ

โครงการนี้ใช้เพื่อดำเนินการสลักพัลซิ่งที่ประหยัดพลังงานและประสิทธิภาพสูงซึ่งส่วนใหญ่ใช้สำหรับระบบ VLSI โดยใช้โทโพโลยีใหม่ เนื่องจากโทโพโลยีนี้ส่วนใหญ่ขึ้นอยู่กับขั้นตอนสุดท้ายที่ผลัก - ดึงโดยใช้สองช่องทางแบ่งผ่านเครื่องกำเนิดพัลส์แบบมีเงื่อนไข

23). Arithmetic Coder VLSI Architecture ใน SPIHT

ระบบที่นำเสนอนี้ช่วยเพิ่มทรูพุตของวิธีการเขียนโค้ดเลขคณิตในการบีบอัดชุดแบ่งพาร์ติชันในต้นไม้ลำดับชั้น (SPIHT) ด้วยสถาปัตยกรรมความเร็วสูงขึ้นอยู่กับ FPGA

24). การลดสัญญาณรบกวนของสัญญาณ ECG ตาม FPGA

โครงการนี้ใช้เพื่อควบคุมสัญญาณรบกวนภายในสัญญาณ ECG ผ่านตัวกรองค่ามัธยฐานสองตัวที่มีขนาดจุดตัวอย่าง 91 และ 7 ตามลำดับ ดังนั้นกระบวนการนี้สามารถบรรลุได้โดยการใช้ การออกแบบ FPGA ขึ้นอยู่กับรหัส VHDL

25). โปรเซสเซอร์ปรับขนาดภาพประสิทธิภาพสูงที่ใช้ VLSI พร้อมต้นทุนต่ำ

โครงการนี้ใช้เพื่อใช้อัลกอริทึมสำหรับตัวประมวลผลการปรับขนาดภาพตาม VLSI ที่มีหน่วยความจำน้อยและประสิทธิภาพสูง การออกแบบระบบที่นำเสนอส่วนใหญ่ประกอบด้วยการรวมตัวกรองวิธีการแบบไดนามิกที่กำหนดค่าใหม่ได้และการแบ่งปันฮาร์ดแวร์เพื่อลดต้นทุน

26). การออกแบบและการใช้งานสถาปัตยกรรม Systolic Array อย่างมีประสิทธิภาพ

แนวคิดหลักของโครงการนี้คือการออกแบบโมเดลฮาร์ดแวร์ที่ใช้สำหรับตัวคูณอาร์เรย์ซิสโตลิก อาร์เรย์นี้สามารถใช้เพื่อดำเนินการคูณไบนารีเป็นหลักด้วยความช่วยเหลือของแพลตฟอร์ม VHDL การออกแบบระบบที่นำเสนอสามารถดำเนินการได้โดยใช้ซอฟต์แวร์ FPGA & Isim

27). QPSK Design & Synthesis โดยใช้ VHDL Code

QPSK เป็นวิธีการมอดูเลตหลักวิธีหนึ่ง วิธีนี้ใช้ในการใช้งานวิทยุดาวเทียม เทคนิคการมอดูเลตนี้สามารถนำไปใช้ผ่านประตูลอจิกแบบย้อนกลับได้ การออกแบบเทคนิค QPSK สามารถทำได้ด้วยความช่วยเหลือของรหัส VHDL

28). DDR SDRAM Controller Design & Implementation with High Speed

ระบบที่นำเสนอใช้ในการออกแบบคอนโทรลเลอร์ DDR SDRAM สำหรับการถ่ายโอนข้อมูลต่อเนื่องขึ้นอยู่กับความเร็วสูงในการซิงโครไนซ์ข้อมูลนี้ระหว่างวงจรของระบบฝังตัวและ DDR SDRAM โดยใช้ภาษา VHDL สามารถพัฒนาโค้ดได้

29). การออกแบบและการใช้งานโปรเซสเซอร์ RISC 32 บิต

แนวคิดหลักของโครงการนี้คือการใช้ 32 บิต RISC (คอมพิวเตอร์ชุดคำสั่งแบบย่อ) ด้วยความช่วยเหลือของเครื่องมือเช่น XILINK VIRTEX4 ในโครงการนี้ชุดคำสั่ง 16 ชุดได้รับการออกแบบทุกคำสั่งสามารถดำเนินการในรอบ CLK เดียวโดยใช้วิธีการไปป์ไลน์ห้าเฟส

30). การใช้งาน Bus Bridge ระหว่าง AHB และ OCP

ระบบที่นำเสนอนี้ใช้ในการออกแบบบัสบริดจ์ระหว่างสองโปรโตคอลคือ common & standard โปรโตคอลการสื่อสารเช่น AHB (Advanced High-performance Bus) & OCP (Open Core Protocol) เป็นที่นิยมมากซึ่งใช้ในแอปพลิเคชันของ SoC (ระบบบนชิป) .

แนวคิดโครงการ VLSI สำหรับนักศึกษาวิศวกรรม

รายชื่อโครงการ VLSI ตาม FPGA, MatLab, IEEE และ Mini Projects สำหรับนักศึกษาวิศวกรรมอยู่ด้านล่าง

โครงการ VLSI สำหรับนักเรียน M. Tech

รายชื่อโครงการ VLSI ตาม M. Tech Students มีดังต่อไปนี้

- การออกแบบเซลล์หน่วยความจำ I0T ตามมาตรฐาน RHBD ที่มีประสิทธิภาพและเชื่อถือได้สูงที่ใช้ในแอปพลิเคชันด้านการบินและอวกาศ

- เครื่องตรวจจับเฟสที่มีอัตราครึ่งระดับหลายระดับที่ใช้สำหรับวงจร CLK และการกู้คืนข้อมูล

- เครื่องเปรียบเทียบด้วยพลังงานต่ำและความเร็วสูงที่ใช้สำหรับการใช้งานที่แม่นยำ

- ตัวแปลระดับแรงดันไฟฟ้าแบบ Gated พร้อม Multiplexer ประสิทธิภาพสูงและในตัว

- Ternary Adder ที่ใช้ CNTFET พร้อมประสิทธิภาพสูง

- การออกแบบเครื่องเปรียบเทียบขนาดด้วยพลังงานต่ำ

- การออกแบบ Threshold Logic Gate พร้อมโหมดปัจจุบันสำหรับการวิเคราะห์ความล่าช้า

- ตัวถอดรหัสสัญญาณแบบผสม - ลอจิกออกแบบด้วยพลังงานต่ำและประสิทธิภาพสูง

- การออกแบบการทดสอบลอจิกของ Sleep Convention

- ตัวเปลี่ยนระดับแรงดันไฟฟ้าสำหรับแอปพลิเคชั่นแหล่งจ่ายคู่ที่มีความเร็วสูงและมีประสิทธิภาพพลังงาน

- การออกแบบและวิเคราะห์เครื่องเปรียบเทียบสองหางกำลังต่ำและแรงดันต่ำ

- การออกแบบ Flip-Flop ขึ้นอยู่กับ Pulse-Triggered ด้วยพลังงานต่ำโดยใช้วิธีป้อนสัญญาณ

- การออกแบบวงจรที่มีประสิทธิภาพขึ้นอยู่กับ FET ที่กำหนดค่าได้ของรันไทม์

- การออกแบบเครื่องเปรียบเทียบขนาดด้วยพลังงานต่ำ

- การวิเคราะห์ความล่าช้าของการออกแบบลอจิกเกทด้วยเกณฑ์โหมดปัจจุบัน

โครงการ VLSI ที่ใช้ FPGA สำหรับนักศึกษาวิศวกรรมและ CMOS VLSI ออกแบบมินิโปรเจ็กต์ อยู่ด้านล่าง

- SEU Hardened Circuits Design & Characterization สำหรับ FPGA ตาม SRAM

- Compact Memristor ที่ใช้ CMOS hybrid LUT Design & Potential Application ที่ใช้ใน FPGA

- การใช้เซ็นเซอร์อัลตราโซนิกโดยใช้ FPGA สำหรับการวัดระยะทาง

- การใช้งาน FPGA สำหรับ Booth Multiplier ด้วย Spartan6 FPGA

- การแปลงเวฟเล็ตแบบแยกตามการยกด้วย Spartan3 FPGA

- ARM Controller ในหุ่นยนต์โดยใช้ FPGA

- UART ที่ใช้ FPGA พร้อมหลายช่องทาง

- การปราบปรามสัญญาณรบกวนคลื่นไฟฟ้าหัวใจโดยใช้ FPGA

- การใช้งาน FPGA ตาม UTMI และเลเยอร์โปรโตคอล USB 2.0

- การติดตั้ง Median Filter กับ Spartan3 FPGA

- AES อัลกอริทึมการใช้งานตาม FPGA

- ระบบแจ้งเตือนความปลอดภัยตาม PIC สำหรับการนำ FPGA ไปใช้กับ Spartan 3an

- การใช้ FPGA เพื่อออกแบบคอนโทรลเลอร์สำหรับระบบสำรวจระยะไกล

- ชุดประมวลผลภาพของ FPGA โดยใช้การกรองภาพของ Linear & Morphological

- Spartan3 FPGA โดยใช้ Medical Fusion Image Implementation

รายการของ โครงการขนาดเล็ก VLSI โดยใช้รหัส VHDL รวมถึงสิ่งต่อไปนี้

- เครื่องเปรียบเทียบด้วยความเร็วสูงโดยใช้ VLSI

- ตัวคูณของ Floating-Point โดยใช้ VLSI

- การแปลงไบนารีเป็นสีเทาตาม VLSI

- ตัวกรองดิจิตอล

- CLK Gating ขึ้นอยู่กับ VLSI

- ตัวคูณเวท

- CMOS FF โดยใช้ VLSI

- สถาปัตยกรรมของโปรเซสเซอร์แบบขนานโดยใช้ VLSI

- VLSI ตาม Full Adder

- การออกแบบ DRAM / Dynamic Random Access Memory ตาม VLSI

- SRAM Layout ขึ้นอยู่กับ VLSI

- โปรเซสเซอร์สัญญาณดิจิทัลที่ใช้ VLSI

- Multiplexer ที่ใช้ VLSI

- การออกแบบหน่วย MAC ตาม VLSI

- VLSI ตามความแตกต่าง

- FFT ที่ใช้ VLSI หรือ Fast Fourier Transform

- สถาปัตยกรรมของการแปลงโคไซน์แบบไม่ต่อเนื่องตาม VLSI

- การออกแบบตัวคูณ 16 บิตโดยใช้ VLSI19

- การออกแบบตาม VLSI ของ FIFO Buffer

- ตัวเร่งความเร็วสูงขึ้นอยู่กับ VLSI

โครงการ VLSI โดยใช้ MATLAB & Xilinx

รายการโครงการ VLSI ที่ยึดตามโครงการ MATLAB และ VLSI ที่ใช้ Xilinx มีดังต่อไปนี้

- การออกแบบและวิเคราะห์โมเด็ม CDMA ด้วย MATLAB

- การออกแบบตัวกรอง FIR โดยใช้ VHDL บนการวิเคราะห์ตาม FPGA & MATLAB

- ModelSim & Matlab หรือ Simulink ตามการจำลองระบบสำหรับวิศวกรรมยานยนต์

- Xilinx จาก Adders เช่น Ripple Carry & Carry Skip

- หน่วยเลขคณิตขึ้นอยู่กับ Floating Point 32 บิต

- ALU ตามจุดลอยตัว

- RISC โปรเซสเซอร์ที่ใช้ 32 บิต

- ความสามารถในการแปลงของรหัสมุมฉาก

- Xilinx และ Verilog จากเครื่องจำหน่ายสินค้าอัตโนมัติ

- Xilinx ที่ใช้ Parallel Prefix Adders พร้อม 256 บิต

- โปรโตคอลสำหรับการพิสูจน์ตัวตนร่วมกันโดยใช้ Xilinx

- โครงสร้างการเข้าถึงด้วยวงจรเดียวสำหรับการทดสอบลอจิกโดยใช้ Xilinx

- UTMI & Protocol Layer ที่ใช้ USB2.0 โดยใช้ Xilinx

- การกำหนดค่าการบีบอัดข้อมูลและการบีบอัดข้อมูลโดยใช้ Xilinx FPGA

- Xilinx 4000 ที่ใช้ BIST และ Spartan Series ที่ใช้ FPGA

- IIR Filter ขึ้นอยู่กับ MATLAB & VLSI

- FIR Filter โดยใช้ MATLAB

โครงการ IEEE

รายชื่อโครงการ IEEE VLSI อยู่ด้านล่าง

- ระบบบ้านอัตโนมัติไร้สายที่ใช้ VLSI โดยใช้บลูทู ธ

- การลบ Impulse Noise ภายในภาพโดยใช้สถาปัตยกรรมที่มีประสิทธิภาพของ VLSI

- สถาปัตยกรรมของโปรเซสเซอร์ในหน่วยความจำสำหรับการบีบอัดมัลติมีเดีย

- การตรวจสอบระบบอุณหภูมิโดยใช้ Cloud & IoT

- การติดตั้งระบบ OFDM ด้วย IFFT & FFT

- Hamming Code Design & Implementation with Verilog

- การจดจำลายนิ้วมือที่ใช้ VHDL โดยใช้ Gabor Filter

- ฟังก์ชันเลขคณิตรีแมปกับ ROM ขึ้นอยู่กับวิธีการประมาณ

- การวิเคราะห์ประสิทธิภาพสูงและประสิทธิภาพความหนาแน่นต่ำของตัวถอดรหัสรหัสตรวจสอบความเท่าเทียมกันในการใช้งานที่ใช้พลังงานต่ำ

- สถาปัตยกรรม FFT พร้อม Feedforward ของ Radix-2k แบบท่อ

- การออกแบบรองเท้าแตะสำหรับแอปพลิเคชัน VLSI โดยใช้เทคโนโลยี CMOS ที่มีประสิทธิภาพสูง

- การออกแบบตัวกรอง FIR พร้อมตารางการค้นหาโดยการกระจายเลขคณิต

- ต้นทุนต่ำที่ใช้ VLSI และโปรเซสเซอร์การปรับขนาดภาพขั้นสูง

- การใช้งาน ASIC และการออกแบบตัวเข้ารหัสและตัวถอดรหัส Advance Turbo พร้อม 3GPP LTE

- Push-Pull Pulsed Latches พร้อมเงื่อนไขการใช้พลังงานต่ำและความเร็วสูง

- การสแกนขั้นสูงในการทดสอบการสแกนด้วยพลังงานต่ำ

- Arithmetic Coder VLSI Architecture สำหรับ SPIHT

- การใช้งาน VHDL สำหรับ UART

- ตัวควบคุมแรงดันไฟฟ้าที่ใช้ VLSI พร้อมการปล่อยต่ำ

- การออกแบบ Flash ADC พร้อม Enhanced Comparator Scheme

- การออกแบบตัวคูณพลังงานต่ำพร้อมสไตล์ลอจิกคงที่แบบคงที่

- เครื่องเปรียบเทียบหางคู่ที่มีประสิทธิภาพสูงและใช้พลังงานต่ำ

- ระบบจัดเก็บข้อมูลแฟลชที่มีประสิทธิภาพสูงขึ้นอยู่กับบัฟเฟอร์การเขียนและหน่วยความจำเสมือน

- FF พลังงานต่ำตามแนวทาง Sleepy Stack

- LFSR Power Optimization สำหรับ BIST พลังงานต่ำที่ใช้ใน HDL

- การออกแบบและการใช้งานเครื่องหยอดเหรียญด้วย Verilog HDL

- การออกแบบตัวสะสมตามการสร้างรูปแบบ 3 น้ำหนักด้วย LP-LSFR

- เครื่องถอดรหัส Reed-Solomon พร้อมความเร็วสูงและความซับซ้อนต่ำ

- เทคนิคการออกแบบตัวคูณ Dadda ที่เร็วขึ้น

- Digital Demodulation ตามตัวรับของวิทยุ FM

- การสร้างรูปแบบการทดสอบด้วย BIST Schemes

- การนำสถาปัตยกรรม VLSI ไปใช้กับท่อส่งความเร็วสูง

- การออกแบบโปรโตคอล OCP บนชิปบัสโดยใช้ฟังก์ชันบัส

- เครื่องตรวจจับความถี่เฟสและการออกแบบปั๊มชาร์จที่ใช้สำหรับลูปล็อคเฟสความถี่สูง

- การออกแบบหน่วยความจำแคชและตัวควบคุมแคชด้วย VHDL

- ASTRAN ตามการใช้งานของ Low Power 3-2 & 4-2 Adder Compressors

- ระบบการเรียกเก็บเงินค่าไฟฟ้าแบบเติมเงินโดยใช้การออกแบบบนชิป

- การใช้งานที่ทับซ้อนกันโดยใช้เซลล์ลอจิกและการวิเคราะห์พลังงาน

- พก Look Ahead Adder ด้วยการวิเคราะห์ประสิทธิภาพบิตที่แตกต่างกันโดยใช้ VHDL

- การออกแบบ Data Link Layer พร้อม Wi-Fi MAC โปรโตคอล

- การปรับใช้ FPGA สำหรับโปรโตคอลการพิสูจน์ตัวตนร่วมกับ Modular Arithmetic

- การสร้างสัญญาณ PWM โดยใช้ FPGA & Variable Duty Cycle

โครงการตามเวลาจริง

รายการของ โครงการเรียลไทม์ VLSI ส่วนใหญ่ประกอบด้วยโครงการขนาดเล็ก VLSI โดยใช้รหัส VHDL และโครงการซอฟต์แวร์ VLSI สำหรับนักศึกษาวิศวกรรม ECE

- การรวมในทางปฏิบัติของ SRAM Row Cache ในสถาปัตยกรรม DRAM 3 มิติที่แตกต่างกันโดยใช้ TSV

- เทคนิคการทดสอบตัวเองในตัวสำหรับการวินิจฉัยข้อผิดพลาดของการหน่วงเวลาในอาร์เรย์เกทที่ตั้งโปรแกรมฟิลด์ตามคลัสเตอร์

- การออกแบบ ASIC ของตัวคูณที่ซับซ้อน

- การติดตั้ง VLSI ต้นทุนต่ำเพื่อการกำจัดเสียงอิมพัลส์อย่างมีประสิทธิภาพ

- ตาม FPGA Space Vector PWM IC ควบคุมสำหรับมอเตอร์เหนี่ยวนำสามเฟส

- การใช้งาน VLSI ของ Auto Correlator และ CORDIC Algorithm สำหรับ OFDM Based WLAN

- การสกัดถนนอัตโนมัติโดยใช้ภาพดาวเทียมความละเอียดสูง

- การออกแบบ VHDL สำหรับการแบ่งส่วนภาพโดยใช้ Gabor Filter สำหรับการตรวจหาโรค

- สถาปัตยกรรมตัวถอดรหัสเทอร์โบที่มีความซับซ้อนต่ำสำหรับเครือข่ายเซนเซอร์ไร้สายที่ประหยัดพลังงาน

- การปรับปรุงความสามารถในการแปลงรหัส Orthogonal โดยใช้ FPGA Implementation

- การออกแบบและการติดตั้ง Floating Point ALU

- การออกแบบ CORDIC สำหรับมุมการหมุนคงที่

- รหัสผลิตภัณฑ์ Reed-Solomon สำหรับการติดตั้ง NAND Flash Controller บนชิป FPGA

- การปรับปรุงอัตราผลตอบแทนการเข้าถึงการอ่าน SRAM ทางสถิติโดยใช้วงจรประจุลบ

- การจัดการพลังงานของการเชื่อมต่อเครือข่าย MIMO บนระบบมือถือ

- การออกแบบมาตรฐานการเข้ารหัสข้อมูลสำหรับการเข้ารหัสข้อมูล

- ใช้พลังงานต่ำและมีประสิทธิภาพในพื้นที่เลือก Adder

- การสังเคราะห์และการใช้งาน UART โดยใช้รหัส VHDL

- ปรับปรุงสถาปัตยกรรมสำหรับหน่วยเพิ่ม - ลบจุดลอยตัวแบบหลอมรวม

- เครื่องส่งสัญญาณดิจิตอลทั้งหมด 1 บิตที่ใช้ FPGA ซึ่งใช้การมอดูเลต Delta-Sigma พร้อมเอาต์พุต RF สำหรับ SDR

- การเพิ่มประสิทธิภาพการใช้งานการค้นหาลูกโซ่ในตัวถอดรหัส BCH สำหรับการส่งอัตราความผิดพลาดสูง

- การออกแบบเครื่องส่ง DS-CDMA แบบดิจิทัลโดยใช้ Verilog HDL และ FPGA

- การออกแบบและการใช้งานสถาปัตยกรรม Systolic Array ที่มีประสิทธิภาพ

- อัลกอริทึมการเรียนรู้พลวัตของหุ่นยนต์ที่ใช้ VLSI

- การออกแบบหน่วยฟังก์ชันมัลติมีเดียที่หลากหลายโดยใช้เทคนิคการปราบปรามพลังงานปลอม

- การออกแบบ Bus Bridge ระหว่าง AHB และ OCP

- การสังเคราะห์เชิงพฤติกรรมของวงจรอะซิงโครนัส

- การเพิ่มประสิทธิภาพความเร็วของตัวถอดรหัส Viterbi ดัดแปลงตาม FPGA

- การใช้งานอินเทอร์เฟซ I2C

- ตัวคูณความเร็วสูง / พลังงานต่ำโดยใช้เทคนิคการปราบปรามพลังงานปลอมขั้นสูง

- การจับแรงดันจ่ายเสมือนของวงจรไฟฟ้าที่มีรั้วรอบขอบชิดสำหรับการลดการรั่วไหลที่ใช้งานอยู่และความน่าเชื่อถือของเกทออกไซด์

- FPGA Based Power Efficient Channelizer สำหรับซอฟต์แวร์ที่กำหนดวิทยุ

- สถาปัตยกรรม VLSI และการสร้างต้นแบบ FPGA ของกล้องดิจิทัลเพื่อความปลอดภัยของภาพและการพิสูจน์ตัวตน

- การปรับปรุงการทำงานของหุ่นยนต์ในร่ม

- การออกแบบและการใช้งานเครือข่ายการเรียงสับเปลี่ยน ON-Chip สำหรับระบบมัลติโปรเซสเซอร์บนชิป

- วิธีการซิงโครไนซ์ไทม์มิ่งอัตราสัญลักษณ์สำหรับระบบ OFDM ไร้สายพลังงานต่ำ

- DMA Controller (การเข้าถึงหน่วยความจำโดยตรง) โดยใช้ VHDL / VLSI

- FFT ที่กำหนดค่าใหม่ได้โดยใช้สถาปัตยกรรมที่ใช้ CORDIC สำหรับเครื่องรับ MIMI-OFDM

- เทคนิคการปราบปรามพลังงานปลอมสำหรับแอปพลิเคชันมัลติมีเดีย / DSP

- ประสิทธิภาพของรหัส BCH ใน Digital Image Watermarking

- ตัวควบคุม SD-RAM อัตราข้อมูลคู่

- การใช้ Gabor Filter สำหรับการจดจำลายนิ้วมือโดยใช้ Verilog HDL

- การออกแบบ Redundant ของเครื่องชั่งนาโนเมตรที่ใช้งานได้จริงผ่าน Aware Standard Cell Library เพื่อปรับปรุงความซ้ำซ้อนด้วยอัตราการแทรก 1

- อัลกอริทึมการบีบอัดข้อมูลและการบีบอัดข้อมูลแบบไม่สูญเสียข้อมูลและสถาปัตยกรรมฮาร์ดแวร์

- กรอบสำหรับการแก้ไขข้อผิดพลาดแบบหลายบิต

- การบีบอัดข้อมูลทดสอบประสิทธิภาพโดยใช้ Viterbi

- การใช้งาน FFT / IFFT Blocks สำหรับ OFDM

- การบีบอัดภาพโดยใช้ Wavelet โดย VLSI Progressive Coding

- การใช้งาน VLSI ของตัวคูณที่กำหนดท่อเต็มรูปแบบน้อยกว่า 2d DCT / IDCT Architecture สำหรับ Jpeg

- FPGA-Based Fault Emulation ของวงจรลำดับซิงโครนัส

ดังนั้นนี่คือรายชื่อโครงการ VLSI สำหรับวิศวกรรมนักศึกษา M.Tech ซึ่งมีประโยชน์ในการเลือกหัวข้อโครงการปีสุดท้ายของพวกเขา หลังจากใช้เวลาอันมีค่าของคุณในการอ่านรายการนี้เราเชื่อว่าคุณมีความคิดที่ดีพอสมควรในการเลือกหัวข้อโครงการที่คุณเลือกจากรายการโครงการ VLSI และหวังว่าคุณจะมีความมั่นใจเพียงพอที่จะรับหัวข้อใด ๆ จาก รายการ. สำหรับรายละเอียดเพิ่มเติมและความช่วยเหลือเกี่ยวกับโครงการเหล่านี้คุณสามารถเขียนถึงเราได้ในส่วนความคิดเห็นด้านล่าง นี่คือคำถามสำหรับคุณ VHDL คืออะไร?

เครดิตภาพ

- โครงการ VLSI โดย ชุดเทคโนโลยี