ECL (ตรรกะคู่ของอีซีแอล) ถูกประดิษฐ์ขึ้นครั้งแรกที่ IBM ในเดือนสิงหาคม 1956 โดย Hannon S. Yourke ลอจิกนี้เรียกอีกอย่างว่าลอจิกโหมดปัจจุบัน ซึ่งใช้ในคอมพิวเตอร์ของ IBM 7090 & 7094 ตระกูล ECL นั้นเร็วมากเมื่อเทียบกับ ตรรกะดิจิทัล ครอบครัว โดยทั่วไป ลอจิกแฟมิลีนี้มีความล่าช้าในการแพร่กระจายน้อยกว่า 1 ns เป็นตระกูลลอจิกที่ยึดตามทรานซิสเตอร์สองขั้วทางแยก เป็นวงจรตระกูลลอจิกที่เร็วที่สุดที่สามารถเข้าถึงได้สำหรับการออกแบบระบบลอจิกทั่วไป บทความนี้กล่าวถึงภาพรวมของ an อีซีแอลลอจิกคู่-วงจร ,การทำงานกับแอพพลิเคชั่น

อีซีแอลลอจิกคู่คืออะไร?

ตรรกะควบคู่ไปกับอีซีแอลนั้นดีที่สุด BJT ตระกูลลอจิกแบบอิงที่ใช้ในการออกแบบระบบลอจิกแบบเดิม บางครั้งเรียกอีกอย่างว่าตรรกะของโหมดปัจจุบันซึ่งเป็นเทคโนโลยีดิจิตอลความเร็วสูงมาก โดยทั่วไปแล้ว ECL ถือเป็น IC ลอจิกที่เร็วที่สุด โดยสามารถทำงานด้วยความเร็วสูงได้โดยใช้แรงดันไฟฟ้าที่แกว่งเล็กน้อย และหลีกเลี่ยงไม่ให้ทรานซิสเตอร์เข้าสู่บริเวณอิ่มตัว

การนำ ECL ไปใช้นั้นใช้แรงดันไฟฟ้าที่เป็นบวกซึ่งเรียกว่า PECL หรือ ECL ที่อ้างอิงเชิงบวก ในเกท ECL ยุคแรก การจ่ายแรงดันไฟลบจะถูกใช้เนื่องจากการกันเสียง หลังจากนั้น ECL ที่อ้างอิงในเชิงบวกก็มีชื่อเสียงมากเนื่องจากมีระดับตรรกะที่เข้ากันได้มากกว่าเมื่อเปรียบเทียบกับตระกูลตรรกะ TTL

ตรรกะที่ควบคู่ไปกับอีซีแอลจะกระจายพลังงานสถิตจำนวนมาก อย่างไรก็ตาม การใช้กระแสไฟโดยรวมนั้นต่ำเมื่อเทียบกับ CMOS ที่ความถี่สูง ดังนั้น ECL จึงมีประโยชน์อย่างมากในวงจรการกระจายสัญญาณนาฬิกาและแอพพลิเคชั่นที่ใช้ความถี่สูง

คุณสมบัติลอจิกคู่ Emitter

คุณสมบัติของ ECL จะทำให้ใช้งานได้ในแอปพลิเคชันที่มีประสิทธิภาพสูงมากมาย

- ECL ให้เอาท์พุตสองเอาต์พุตซึ่งเสริมซึ่งกันและกันเสมอ เพราะการทำงานของวงจรนั้นขึ้นอยู่กับแอมพลิฟายเออร์ดิฟเฟอเรนเชียล

- ตระกูลลอจิกนี้เหมาะอย่างยิ่งสำหรับวิธีการประดิษฐ์เสาหินเนื่องจากระดับลอจิกเป็นฟังก์ชันของอัตราส่วนตัวต้านทาน

- อุปกรณ์ของตระกูล ECL จะสร้างเอาต์พุตที่ถูกต้องและเสริมของฟังก์ชันที่เสนอโดยไม่ต้องใช้อินเวอร์เตอร์ภายนอก ส่งผลให้จำนวนแพ็คเกจลดลง ความต้องการพลังงานลดลง และยังช่วยลดปัญหาที่เกิดจากความล่าช้าอีกด้วย

- อุปกรณ์ ECL ในการออกแบบแอมพลิฟายเออร์ดิฟเฟอเรนเชียลให้ความยืดหยุ่นด้านประสิทธิภาพในวงกว้าง ดังนั้นวงจร ECL จึงอนุญาตให้ใช้เป็นวงจรทั้งแบบดิจิตอลและเชิงเส้น

- การออกแบบประตู ECL มีอิมพีแดนซ์อินพุตสูงและต่ำตามปกติ ซึ่งเอื้ออย่างยิ่งต่อการรับพัดลมออกขนาดใหญ่และความสามารถของไดรฟ์

- อุปกรณ์ ECL สร้างการระบายกระแสไฟคงที่บนแหล่งจ่ายไฟเพื่อให้การออกแบบแหล่งจ่ายไฟง่ายขึ้น

- อุปกรณ์ของ ECL รวมถึงเอาท์พุตอีซีแอลแบบเปิดช่วยให้สามารถรวมความจุของไดรฟ์สายส่งได้

วงจรลอจิกคู่อีซีแอล

วงจรลอจิกควบคู่กับอีซีแอลสำหรับอินเวอร์เตอร์แสดงไว้ด้านล่างซึ่งออกแบบด้วยตัวต้านทานและทรานซิสเตอร์ ในวงจรนี้ ขั้วอีซีแอลของทรานซิสเตอร์สองตัวเชื่อมต่อกันอย่างง่ายๆ กับความต้านทานจำกัดกระแส RE ซึ่งใช้เพื่อหลีกเลี่ยงไม่ให้ทรานซิสเตอร์เข้าสู่ความอิ่มตัว ที่นี่เอาต์พุตของทรานซิสเตอร์ถูกนำมาจากเทอร์มินัลสะสมแทนเทอร์มินัลอีซีแอล วงจรนี้มีเอาต์พุตสองแบบคือ Vout (เอาต์พุตกลับด้าน) และ Vout2 (เอาต์พุตที่ไม่กลับด้าน) และขั้วอินพุตเช่น Vin ที่ให้อินพุตสูงหรือต่ำ +Vcc = 5V.

ลอจิกคู่ Emitter ทำงานอย่างไร?

การทำงานของลอจิกคู่ของอีซีแอลคือ เมื่อใดก็ตามที่อินพุต HIGH ให้กับวงจร ECL จะทำให้ทรานซิสเตอร์ 'Q1' เปิดและทรานซิสเตอร์ Q2 ปิด แต่ทรานซิสเตอร์ Q1 นั้นไม่อิ่มตัว ดังนั้นสิ่งนี้จะดึงเอาต์พุต VOUT2 ไปที่ HIGH และค่าของเอาต์พุต VOUT1 จะต่ำเนื่องจากการดรอปภายใน R1

ในทำนองเดียวกัน เมื่อค่า VIN ที่กำหนดให้ ECL เป็น LOW จะทำให้ทรานซิสเตอร์ Q1 ปิด และเปิดทรานซิสเตอร์ Q2 ดังนั้นทรานซิสเตอร์ Q2 จะไม่เคลื่อนเข้าสู่ความอิ่มตัว ดังนั้นมันจะทำให้เอาต์พุต VOUT1 ถูกดึงค่า HIGH และค่าเอาต์พุต VOUT2 จะต่ำเนื่องจากการดรอปภายในความต้านทาน R2

มาดูกันว่าทรานซิสเตอร์ Q1 และ Q2 เปิดและปิดอย่างไรเมื่อใช้แรงดันไฟฟ้า

ทรานซิสเตอร์สองตัวเช่น Q1 & Q2 ในวงจรนี้เชื่อมต่อกันเป็นแอมพลิฟายเออร์ดิฟเฟอเรนเชียลโดยใช้ตัวต้านทานอีซีแอลทั่วไป

แหล่งจ่ายแรงดันไฟสำหรับวงจรตัวอย่างนี้คือ VCC = 5.0, VBB = 4.0 & VEE = 0 V. ค่าอินพุต HIGH & LOW-level ถูกกำหนดเป็น 4.4 V & 3.6V อันที่จริงวงจรนี้สร้างเอาต์พุต LOW และ HIGH ที่สูงกว่า 0.6 โวลต์; อย่างไรก็ตาม สิ่งนี้จะได้รับการแก้ไขภายในวงจร ECL จริง

เมื่อ Vin เป็น HIGH ทรานซิสเตอร์ Q1 จะถูกเปิด แต่ไม่อิ่มตัวและทรานซิสเตอร์ Q2 จะถูกปิด ดังนั้นแรงดันเอาต์พุตเช่น VOUT2 จะถูกดึงไปที่ 5 V ผ่านตัวต้านทาน R2 และสามารถแสดงให้เห็นว่าแรงดันตกคร่อมตัวต้านทาน R1 อยู่ที่ประมาณ 0.8 V ดังนั้น VOUT1 = 4.2 V (LOW) นอกจากนี้ VE = VOUT1 – VQ1 => 4.2V – 0.4V = 3.8V เนื่องจากทรานซิสเตอร์ Q1 ถูกเปิดโดยสมบูรณ์

เมื่อ Vin อยู่ในระดับต่ำ ทรานซิสเตอร์ Q2 จะถูกเปิด แต่ไม่อิ่มตัว และทรานซิสเตอร์ Q1 จะถูกปิด ดังนั้น VOUT1 จะถูกดึงไปที่ 5.0 V โดยใช้ตัวต้านทาน R1 และจะแสดงได้ว่า VOUT2 คือ 4.2 V นอกจากนี้ VE => VOUT2 – VQ2 => 4.2V – 0.8V => 3.4V เมื่อเปิดทรานซิสเตอร์ Q2

ใน ECL ทรานซิสเตอร์สองตัวจะไม่อิ่มตัวเท่ากับ t ความผันผวนของแรงดันอินพุต / เอาต์พุตนั้นค่อนข้างเล็กเช่น 0.8v และอิมพีแดนซ์อินพุตสูงและความต้านทานเอาต์พุตต่ำ ซึ่งช่วยให้ ECL ทำงานได้เร็วขึ้นโดยมีเวลาหน่วงในการเผยแพร่น้อยลง

สองอินพุทอีซีแอลลอจิกควบคู่ OR / NOR Gate Circuit

วงจรเกต OR/NOR ของลอจิกอีซีแอลอินพุตสองตัวแสดงอยู่ด้านล่าง วงจรนี้ได้รับการออกแบบโดยการปรับเปลี่ยนวงจรอินเวอร์เตอร์ข้างต้น การปรับเปลี่ยนคือโดยการเพิ่มทรานซิสเตอร์พิเศษที่ด้านอินพุต

การทำงานของวงจรนี้ง่ายมาก เมื่ออินพุตที่ใช้กับทรานซิสเตอร์ทั้ง Q1 และ Q2 ต่ำจะทำให้เอาต์พุต1 (Vout1) เป็นค่าสูง ดังนั้น Vout1 นี้จึงสอดคล้องกับเอาต์พุตของเกต NOR

ในเวลาเดียวกัน ถ้าทรานซิสเตอร์ Q3 เปิดอยู่ จะทำให้เอาท์พุตที่สอง (Vout2) เป็น HIGH ดังนั้นเอาต์พุต Vou2 นี้สอดคล้องกับเอาต์พุตเกต OR

ในทำนองเดียวกัน หากอินพุตทรานซิสเตอร์ Q1 และ Q2 ทั้งคู่มีค่าสูง ทรานซิสเตอร์ Q1 และ Q2 จะเปิดขึ้นและให้เอาต์พุตต่ำที่เทอร์มินัล VOUT1

หากทรานซิสเตอร์ Q3 ปิดอยู่ตลอดการดำเนินการนี้ จะให้เอาต์พุตสูงที่ขั้ว VOUT2 ดังนั้น ตารางความจริงสำหรับเกท OR/NOR แสดงไว้ด้านล่าง

|

อินพุต |

อินพุต | หรือ |

ก็ไม่เช่นกัน |

|

อา |

บี | Y | Y |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

ลักษณะลอจิกคู่อิมิตเตอร์

ลักษณะของ ECL มีดังต่อไปนี้

- เมื่อเปรียบเทียบกับ TTL แล้ว ECL มีเวลาการแพร่กระจายที่เร็วกว่าตั้งแต่ 0.5 ถึง 2 ns แต่การกระจายพลังงานลอจิกคู่ของอีซีแอลจะสูงกว่าเมื่อเปรียบเทียบกับ TTL เช่น 30 mW

- แรงดันไฟฟ้า I/O ของ ECL มีการแกว่งเล็กน้อยเช่น 0.8

- อิมพีแดนซ์อินพุตของ ECL สูงและความต้านทานเอาต์พุตต่ำ ดังนั้นทรานซิสเตอร์จึงเปลี่ยนสถานะอย่างรวดเร็ว

- ความสามารถในการกระจาย ECLs สูงและความล่าช้าของเกตต่ำ

- ตรรกะ o/p ของ ECL เปลี่ยนจากสถานะ LOW เป็นสถานะ HIGH แต่ระดับแรงดันไฟฟ้าสำหรับสถานะเหล่านี้จะแตกต่างกันไประหว่าง TTL & EC

- ภูมิคุ้มกันเสียงของ ECL คือ 0.4V

ข้อดีและข้อเสีย

ดิ ข้อดีของลอจิกควบคู่อีซีแอล มีการกล่าวถึงด้านล่าง

- Fanout ของ ECL คือ 25 ซึ่งดีกว่าเมื่อเทียบกับ TTL และต่ำเมื่อเทียบกับ CMOS

- เวลาหน่วงการแพร่กระจายเฉลี่ยของ ECL คือ 1 ถึง 4 ns ซึ่งดีกว่าเมื่อเปรียบเทียบกับทั้ง CMOS &

- ทีทีแอล. ดังนั้นจึงเรียกว่าเป็นตระกูลตรรกะที่เร็วที่สุด

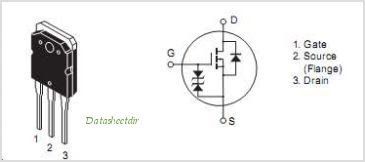

- เมื่อ BJTs ในตัวปล่อยคู่กัน ประตูตรรกะ ทำงานในพื้นที่ที่ใช้งานแล้วพวกเขามีความเร็วสูงสุดเมื่อเทียบกับตระกูลลอจิกทั้งหมด

- ประตู ECL สร้างเอาต์พุตเสริม

- สวิตชิ่งสไปค์ในปัจจุบันไม่มีอยู่ในสายไฟ

- สามารถเชื่อมต่อเอาท์พุตร่วมกันเพื่อให้มีฟังก์ชันมีสาย-OR

- พารามิเตอร์ของ ECL ไม่เปลี่ยนแปลงมากตามอุณหภูมิ

- หมายเลข ของฟังก์ชันที่สามารถเข้าถึงได้จากชิปตัวเดียวนั้นสูง

ดิ ข้อเสียของตรรกะควบคู่อีซีแอล มีการกล่าวถึงด้านล่าง

- มีระยะขอบของสัญญาณรบกวนที่น้อยกว่ามาก เช่น ±200 mV

- การกระจายพลังงานสูงเมื่อเทียบกับลอจิกเกตอื่นๆ

- ในการเชื่อมต่อกับตระกูลลอจิกอื่น ๆ จำเป็นต้องมีตัวเลื่อนระดับ

- Fanout จำกัดการโหลดแบบ capacitive

- เมื่อเทียบกับ TTL , ประตู ECL มีราคาแพง

- เมื่อเทียบกับ CMOS & TTL การป้องกันสัญญาณรบกวนของ ECL นั้นแย่ที่สุด

แอปพลิเคชั่น

การประยุกต์ใช้ลอจิกควบคู่อีซีแอลมีดังต่อไปนี้

- ลอจิกคู่กับอีซีแอลใช้เป็นลอจิกและเทคโนโลยีอินเทอร์เฟซภายในอุปกรณ์สื่อสารความเร็วสูง เช่น อินเทอร์เฟซตัวรับส่งสัญญาณไฟเบอร์ออปติก เครือข่าย Ethernet และ ATM (โหมดการถ่ายโอนอะซิงโครนัส)

- ECL เป็นตระกูลลอจิกที่มีพื้นฐานมาจาก BJT ซึ่งการทำงานด้วยความเร็วสูงสามารถทำได้โดยใช้แรงดันไฟฟ้าที่ค่อนข้างเล็ก และหลีกเลี่ยงไม่ให้ทรานซิสเตอร์เคลื่อนเข้าสู่บริเวณอิ่มตัว

- ECL ใช้ในการสร้างวงจร ASLT ภายใน IBM 360/91

- ECL หลีกเลี่ยงการใช้ทรานซิสเตอร์แบบสแต็กโดยใช้อคติแบบปลายเดียว i/p และผลตอบรับเชิงบวกระหว่างทรานซิสเตอร์หลักและรองเพื่อให้ได้ฟังก์ชันอินเวอร์เตอร์

- ECL ใช้ในอุปกรณ์อิเล็กทรอนิกส์ที่มีความเร็วสูงมาก

ดังนั้นนี่คือ ภาพรวมของลอจิกคู่อีซีแอล หรือ ECL – วงจร การทำงาน คุณลักษณะ ลักษณะเฉพาะ และการใช้งาน ECL เป็นตระกูลลอจิกที่เร็วที่สุดโดยอิงจาก BJT เมื่อเทียบกับตระกูลลอจิกดิจิทัลอื่นๆ บรรลุการทำงานด้วยความเร็วสูงสุดโดยใช้แรงดันไฟฟ้าแกว่งเล็กน้อย & หลีกเลี่ยงไม่ให้ทรานซิสเตอร์เคลื่อนเข้าสู่บริเวณอิ่มตัว ตระกูลลอจิกนี้ทำให้เกิดความล่าช้าในการแพร่กระจาย 1ns อย่างไม่น่าเชื่อ และในตระกูล ECL ล่าสุด ความล่าช้านี้จะลดลง นี่คือคำถามสำหรับคุณ ชื่ออื่นของ ECL คืออะไร?